RISC-V

RISC-V (pronounced “risk-five”) is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. V is the fifth generation RISC (reduced instruction set computer), which means that it has been four RISC processor prototype chip. Unlike most other ISA designs, the RISC-V ISA is provided under open source licenses that do not require fees to use.

What is Risc-V ?

A number of companies are offering or have announced RISC-V hardware, open source operating systems with RISC-V support are available and the instruction set is supported in several popular software toolchains. Open RISC-V’s official website https://riscv.org/, you will see this introduction: RISC-V: The Free and Open RISC Instruction Set Architecture (ISA)

Each generation of RISC processors is completed under the leadership of the same person, and that is Professor David A. Patterson of the University of California, Berkeley. Contrary to most ISAs, RISC-V ISA can be used free of charge in all desired equipment, allowing anyone to design, manufacture and sell RISC-V chips and software.

Although it is not the first open source instruction set (ISA), it is important because it is the first instruction set architecture that can be designed to select the appropriate instruction set according to the specific scenario. Based on the RISC-V instruction set architecture, server CPUs, home appliance CPUs, industrial control CPUs, and CPUs used in sensors smaller than fingers can be designed.

Notable features of the RISC-V ISA include a load–store architecture, bit patterns to simplify the multiplexers in a CPU, IEEE 754 floating-point, a design that is architecturally neutral, and placing most-significant bits at a fixed location to speed sign extension.[1] The instruction set is designed for a wide range of uses.

It is variable-width and extensible so that more encoding bits can always be added. It supports three word-widths, 32, 64, and 128 bits, and a variety of subsets. The definitions of each subset vary slightly for the three word-widths. The subsets support small embedded systems, personal computers, supercomputers with vector processors, and warehouse-scale 19 inch rack-mounted parallel computers.

What is the benefits of Risc-V ?

1 Completely open source

The RISC-V Foundation does not charge high authorization fees for the use of instruction sets. This Open source adopts the loose BSD protocol, and the enterprise can use it freely. It also allows enterprises to add their own instruction set expansion without having to open and share to achieve differentiated development.

2 Simple architecture

The RISC-V architecture adheres to a simple design philosophy. Reflected:

In the processor field, the mainstream architecture is x86 and ARM architecture. The development process of x86 and ARM architecture is also accompanied by the continuous development and maturity of modern processor architecture technology. As a commercial architecture, in order to maintain the future compatibility of the architecture, it has to retain many outdated definitions, resulting in huge amount of instructions and instruction sets, and it has to keep large numbers of documents too. So it is difficult to develop a new operating system on these architectures or directly develop applications.

On the other hand, RISC-V architecture can completely abandon this kinds of burdens, and easily begin to develop. The basic instruction set of RISC-V is only more than 40, with no more than one hundred modular expansion instructions. The RISC-V specification document is only 145 pages, while the “privileged architecture document” is only 91 pages.

3 Easy to Import and Export to Linux or Unix Operating System

Modern operating systems have done the separation of privilege-level instructions and user-level instructions. Privileged instructions can only be called by the operating system, while user-level instructions can only be called in user mode to ensure the stability of the operating system. RISC-V provides privileged instructions and user-level instructions, and provides detailed information of the RISC-V privileged instruction specifications and RISC-V user-level instruction specifications, so that developers can easily export linux and unix systems to RISC-V platform.

4 Modular design

The RISC-V architecture is not only short and sophisticated, but also its different parts can be organized together in a modular manner, thus trying to meet a variety of different application scenarios through a unified architecture. Users can flexibly choose different combinations of modules to meet the needs of their own customized equipment. For example, for small-area low-power embedded scenarios, users can choose the instruction set of the RV32IC and only use Machine Mode. For high-performance application operating system scenarios, you can choose, for example, the instruction set of RV32IMFDC and use Machine Mode and User Mode.

RISC-V has a modular design, consisting of alternative base parts, with added optional extensions. The ISA base and its extensions are developed in a collective effort between industry, the research community and educational institutions. The base specifies instructions (and their encoding), control flow, registers (and their sizes), memory and addressing, logic (i.e., integer) manipulation, and ancillaries. The base alone can implement a simplified general-purpose computer, with full software support, including a general-purpose compiler.

The standard extensions are specified to work with all of the standard bases, and with each other without conflict. Many RISC-V computers might implement the compact extension to reduce power consumption, code size, and memory use. There are also future plans to support hypervisors and virtualization. Together with a supervisor instruction set extension, S, an RVGC defines all instructions needed to conveniently support a general purpose operating system.

| Name | Description | Version | Status |

|---|---|---|---|

| Base | |||

| RV32I | Base Integer Instruction Set, 32-bit | 2.1 | Frozen |

| RV32E | Base Integer Instruction Set (embedded), 32-bit, 16 registers | 1.9 | Open |

| RV64I | Base Integer Instruction Set, 64-bit | 2.0 | Frozen |

| RV128I | Base Integer Instruction Set, 128-bit | 1.7 | Open |

| Extension | |||

| M | Standard Extension for Integer Multiplication and Division | 2.0 | Frozen |

| A | Standard Extension for Atomic Instructions | 2.0 | Frozen |

| F | Standard Extension for Single-Precision Floating-Point | 2.0 | Frozen |

| D | Standard Extension for Double-Precision Floating-Point | 2.0 | Frozen |

| G | Shorthand for the base and above extensions | N/A | N/A |

| Q | Standard Extension for Quad-Precision Floating-Point | 2.0 | Frozen |

| L | Standard Extension for Decimal Floating-Point | 0.0 | Open |

| C | Standard Extension for Compressed Instructions | 2.0 | Frozen |

| B | Standard Extension for Bit Manipulation | 0.92 | Open |

| J | Standard Extension for Dynamically Translated Languages | 0.0 | Open |

| T | Standard Extension for Transactional Memory | 0.0 | Open |

| P | Standard Extension for Packed-SIMD Instructions | 0.1 | Open |

| V | Standard Extension for Vector Operations | 0.8 | Open |

| N | Standard Extension for User-Level Interrupts | 1.1 | Open |

| H | Standard Extension for Hypervisor | 0.4 | Open |

- ^ Frozen parts are expected to have their final feature set and to receive only clarifications before being ratified.

5 Complete tool chain

For designing a CPU, the tool chain is a window for software developers to interact with the CPU. Without a tool chain, the software developer has high requirements for developing software. Even the software developer cannot make the CPU work. In CPU design, the development of tool chain is a job that requires a huge amount of work.

If RISC-V is used to design chips, chip design companies no longer worry about tool chain issues, just focus on chip design. The RISC-V community has provided a complete tool chain, and the RISC-V Foundation continues to maintain the tool chain. The current RISC-V support has been merged into the main tools, such as compilation tool chain gcc, simulation tool qemu, etc.

6 Open Source Implementation

BOOM: Christopher Celio’s RV64 out-of-order processor implementation. Chisel, BSD Licensed.

BottleRocket: RV32IMC microprocessor. Chisel, Apache Licensed.

bwitherspoon: RV32 microprocessor. SystemVerilog, ISC Licensed.

Clarvi: RISC-V processor for teaching at Cambridge University. SystemVerilog, BSD Licensed.

F32: RV32 microprocessor for FPGA, VHDL, BSD Licensed.

GRVI: Gray Research LLC. RV32 microprocessor optimized for FPGA, commercial licensed.

Hummingbird E200. Two-stage pipeline, the target is to replace Cortex-M0/8051, Verilog, Apache 2.0 licensed.

invicta: RV32 microprocessor of the first-stage pipeline. Verilog, BSD Licensed.

Kamikaze: RV32 microprocessor. Verilog, MIT Liencensed.

KCP53000: RV64 processor implementation of Samuel A. Falvo II. Verilog, MPL Licensed.

nanorv32: 2 machine pipeline RV32 implementation. Verilog, GPLv2 Licensed.

OpenV: Open source microprocessor supporting RV32, Verilog, MIT Licensed, OnChipUIS, from Colombia’s Universidad Industrial de Santander.

ORCA: Open source microprocessor supporting RV32, VHDL, BSD Licensed, VectorBlox.

PicoRV32: Clifford Wolf designed (for FPGA) RV32 microprocessor, Verilog, ISC Licensed.

Potato: RV32 microprocessor for FPGA. VHDL, BSD Licensed.

RI5CY: Open source microprocessor supporting RV32

PULPino: SystemVerilog, Solderpad Licensed, PULP project from Zurich University of Technology and University of Bologna.

River: GNSS Senor Ltd. RV64 processor based on Rocket architecture. VHDL, BSD Licensed.

Rocket: Open source processor supporting RV64/32

Rocket-Chip: Chisel, BSD Licensed, Free chips project, open source project separated by UC Berkeley. [

Freedom: Chisel, a start-up separated from Apache Licensed, SiFive, UC Berkeley.

lowRISC: Chisel+SystemVerilog, Solderpad Licensed, a non-profit organization initiated from Cambridge University.

RoCC: the Rocket customized coprocessor interface A co-processor interface that is closely interconnected with Rocket processors.

RV12: RoaLogic’s RV32 microprocessor. Verilog, RoaLogic non-commercial Licensed.

SCR1: Syntacore’s RV32 open source microprocessor. SystemVerilog, Solerpad Licensed.

SHAKTI: Indian IIT-Madras RISC-V processor series, Bluespec, BSD Licensed.

Sodor: RISC-V processor for teaching. Chisel, BSD Licensed.

uRV: RV32 microprocessor for FPGA. Verilog, LGPLv3 Licensed.

VexRiscv: RV32 microprocessor for FPGA written in SpinalHDL. SpinalHDL, MIT Licensed.

YARVI: RV32I microprocessor designed by Tommy Thorn, Verilog, GPL2v Licensed.

How to learn to RISC-V ?

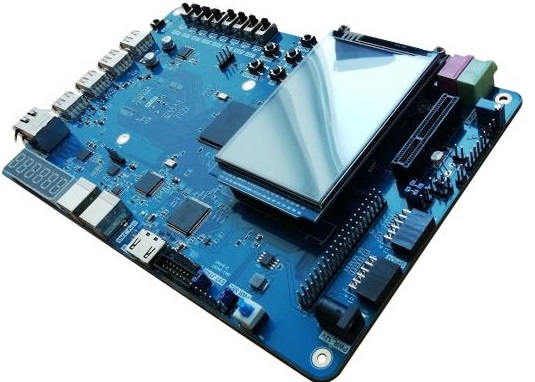

We have three RISC-V Board to teach you learn RISC-V step by step. You can check our RISC-V products in our Product directory.

https://fraserinnovations.com/product-category/risc-v-development-board/

Risc-V Boards, Risc-V FPGA development Boards – RISC-V is an open-source hardware instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. The project began in 2010 at the University of California, Berkeley, but many contributors are volunteers not affiliated with the university. It will become the most popular CPU application soon.

-

Altera Risc-V FPGA Board risc-v SOPC AI Cyclone10 – FII-PRA040 – RiscV Educational Platform

-

RISC-V Board ( ARTIX 100T, XC7A100T ) – FII-PRX100-D – Xilinx Risc-V FPGA Board ( RISC-V SOPC AI Xilinx artix-7 DRAM) -

RISC-V Board ( ARTIX 100T, XC7A100T ) – FII-PRX100-D – Xilinx Risc-V FPGA Board ( RISC-V SOPC AI Xilinx artix-7 DRAM)

-

RISC-V Board ( ARTIX 100T, XC7A100T ) – FII-PRX100-S – Xilinx Risc-V FPGA Board ( riscv SOPC AI Xilinx artix-7 SRAM)

-

Risc-V tutorial

- Altera Risc-V FPGA Tutorial :AD,DA Experiment – FII-PRA040 FPGA Board Experimental 12

- Altera Risc-V FPGA Tutorial : IIC Protocol Transmission – FII-PRA040 FPGA Board Experimental 11

- Altera Risc-V FPGA Tutorial :Asynchronous Serial Port Design and Experiment – FII-PRA040 FPGA Board Experimental 10

- Altera Risc-V FPGA Tutorial : Use Dual-port RAM to Read and Write Frame Data – FII-PRA040 FPGA Board Experimental 9

- Altera Risc-V FPGA Tutorial : Use of ROM – FII-PRA040 FPGA Board Experimental 8

- Altera Risc-V FPGA Tutorial : Hexadecimal Number to BCD Code Conversion and Application – FII-PRA040 FPGA Board Experimental 7

- Altera Risc-V FPGA Tutorial : Use of Multipliers and ModelSim – FII-PRA040 FPGA Board Experimental 6

- Altera Risc-V FPGA Tutorial : Button Debounce – FII-PRA040 FPGA Board Experimental 5

- Altera Risc-V FPGA Tutorial : Block/SCH – FII-PRA040 FPGA Board Experimental 4

- Altera Risc-V FPGA Tutorial : Segment Display – FII-PRA040 FPGA Board Experimental 3

- Altera Risc-V FPGA Tutorial : SignalTap – FII-PRA040 FPGA Board Experimental 2

- Altera Risc-V FPGA Tutorial : LED shifting – FII-PRA040 FPGA Board Experimental 1

- Altera Risc-V FPGA Board Tutorial : Introduction of FII-PRA040 Development System

- Xilinx Risc-V Board Tutorial : HDMI Graphic Display Experiment – FII-PRX100 FPGA Board Experiment 14

- Xilinx Risc-V Board Tutorial : AD, DA Experiment – FII-PRX100 FPGA Board Experiment 13

- Xilinx Risc-V Board Tutorial : IIC Protocol Transmission – FII-PRX100 FPGA Board Experiment 12

- Xilinx Risc-V Board Tutorial : Asynchronous Serial Port Design and Experiment – FII-PRX100 FPGA Board Experiment 11

- Xilinx Risc-V Board Tutorial : Use Dual_port RAM to Read and Write Frame Data – FII-PRX100 FPGA Board Experiment 10

- Xilinx Risc-V Board Tutorial : Use of ROM – FII-PRX100 FPGA Board Experiment 9

- Xilinx Risc-V Board Tutorial : Hexadecimal Number to BCD Code Conversion and Application – FII-PRX100 FPGA Board Experiment 8

- Xilinx Risc-V Board Tutorial : Multiplier Use and ISIM Simulation- FII-PRX100 FPGA Board Experiment 7

- Xilinx Risc-V Board Tutorial : Digital Clock Comprehensive Design Experiment- FII-PRX100 FPGA Board Experiment 6

- Xilinx Risc-V Board Tutorial : Button Debounce Design and Experimental- FII-PRX100 FPGA Board Experiment 5

- Xilinx Risc-V Board Tutorial : Block/SCH Digital Clock Design- FII-PRX100 FPGA Board Experiment 4

- Xilinx Risc-V Board Tutorial : Basic Digital Clock Experiment and Programming of FPGA Configuration Files- FII-PRX100 FPGA Board Experiment 3

- Xilinx Risc-V Board Tutorial : Switches and Display – FII-PRX100 FPGA Board Experiment 2

- Risc-V FPGA Board Xilinx – Development Board Experiment 1 – LED Shifting – FII-PRX100

- xilinx Risc-V FPGA Board – FII-PRX100 – Development System Introduction