We have our own IPcore FII-CPU (RV32G) and it will be taped out soon.

The main features of our IPcore :

- Fully supports the RV32IMFAC instruction architecture and provides a rich set of storage and interfaces, including: ITCM 64K(Instruction Tightly Coupled Memories) and DTCM 64K(Data Tightly Coupled Memories) for separate storage of instructions and data, and 2M bytes External super RAM support as well .

- 3-stage pipeline architecture

- support machine mode only

- From instruction fetch ,Decoder ,Execution to memory operation modules are 100% Manually developed by using pure verilog HDL, scalable and easy to be understood.

- The flexible RISC-V IPCORE is suitable for customized ASIC for specific domain, Also can be used as embedded CPU with in FPGA.

- Interrupt controller, supports 16 high-priority, low-latency local vectored interrupts.

- includes a RISC-V standard PLIC (platform-level interrupt controller ), which supports 127 global interrupts with 7 priority levels. provides the standard RISCV machine-mode timer and software interrupts via the CLINT(Core Local Interruptor)

- 2 UART

- 3 QSPI

- I2C

- 3 PWM

- 10M/100M/1G ethernet

- Watchdog

- 32 GPIO

- 4 7-seg display interface

- External Serial Flash

- Debug Interfaces: JTAG

- 12-Bit ADC

- Four data lines I2S and can support maximum of 8 audio outputs or 4 stereo channels

- Hardware Crypto Engine for Advanced Fast Security, Including: AES 128, CRC, Checksum etc

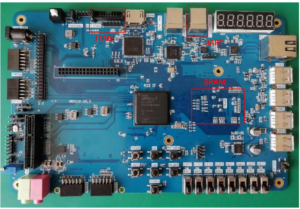

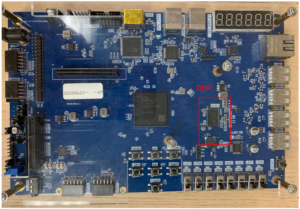

A lot of our Risc-V experiments and our Risc-V courses are based on our own FII-CPU on our FII-PRX100 platform:

- C Programming (2) on RISCV FII-PRX100 (ARTIX-7, XC7A100T) XILINX FPGA Board with our FII-Risc-V CPU (RV32G2.0)

- C Programming (1) on RISCV FII-PRX100 (ARTIX-7, XC7A100T) XILINX FPGA Board with our FII-Risc-V CPU (RV32G2.0)

- Risc-V Bus and PipeLine – FII Risc-V Bus and Pipeline Design – Risc-V Tutorial and Exercise

- FII RISC-V3.01 CPU Processor on FII-PRX100-S (ARTIX-7, XC7A100T) XILINX FPGA Board Evaluation by Coremark and Dhrystone Benchmarks

- Dhrystone Porting Guide For FII RISC-V3.01 CPU Processor on FII-PRX100-S (ARTIX-7, XC7A100T) XILINX FPGA Board

- FII RISC-V3.01 CPU Processor on FII-PRX100-S (ARTIX-7, XC7A100T) XILINX FPGA Board Coremark Porting Guide

- RISC-V Instruction Set Explanation

If you are interested in our Risc-V CPU chips, please contact us.

Visited 1 times, 1 visit(s) today