RISC-V IP CORE FIE310G(RV32G)

FIE310G is a high performance, low power embedded real time RISC-V processor IPCore.

The main application areas aim at smart home, Wearable, sensor Fusion, IOT, and industrial control etc.

Features:

|

|

The entire system is designed by the verilog language, and all IPs can be added, deleted and reconfigured.

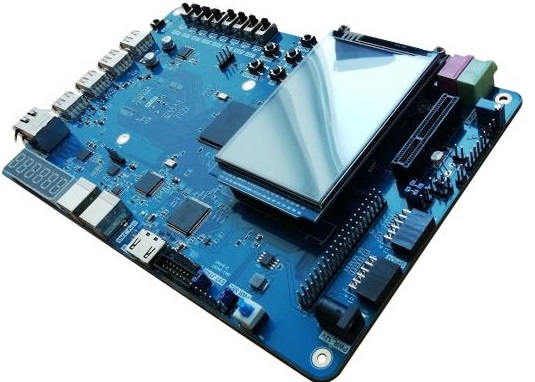

The FII-PRX100 RISC-V development board introduction

- Suitable for FPGA study and training

- Fully support FIE310 CPU running and system development

- Suitable for user customized RV32G verification and validation

- JTAG interface for FPGA and FIE310 CPU download and debug

- Support Windows software and linux development environment

- GCC compilation toolchain and graphical software development environment

- Hardware resource: Switchs, Push Button ,USB to UART convertor, QSPI flash, I2C EEPROM, 100M/1G ethernet, USB keyboard mouse,GPIO , hdmi transmitter and camera etc.

RISC-V IPCore user development Guide

This document is edited by Fraser Innovation Inc. Step by step introduce how to develop each RISC-V CPU RTL modules based on RISC-V ISA, Simulations and board verifications, software environment and details on C language development, debug and program

Fraser Innovation Inc. is a leading FPGA based system design and RF application solution company serving students, college, universities, and OEM’s worldwide with technology-based educational design tools. Based in Richmond, British Columbia, Canada, Fraser Innovation designs, manufactures, and distributes its products on a worldwide basis. We are top wireless communication educational device provider.