Master the Design of the Frequency Divider to Implement the Shifting – LED LED Shifting – Altera Risc-V Board PRA040 Experimental 1

Experiment 1 LED shifting

1.1 Experiment Objective

- Practice to use Quartus II to create new projects and use system resources IP Core;

- Proficiency in the writing of Verilog HDL programs to develop a good code writing style;

- Master the design of the frequency divider to implement the shifting LED;

- Combine hardware resources to perform FPGA pin assignment and implement actual program downloading;

- Observe the experiment result and summarize it.

1.2 Experiment Implement

- Use all LEDS, all light up during reset;

- End reset, LED lights from low to high (from right to left) in turn;

- Each LED is lit for one second;

- After the last (highest position) LED is lit, the next time it returns to the first (lowest position) LED, the loop is achieved;

1.3 Experiment

1.3.1 LED Introduction

LED (Light-Emitting Diode), is characterized by low operating current, high reliability and long life. Up to now, there are many types of LED lights, as shown in Figure 1.1. The FII-PRA040 uses the LED lights in the red circle.

Figure 1.1 Different kinds of LEDs

1.3.2 Hardware Design

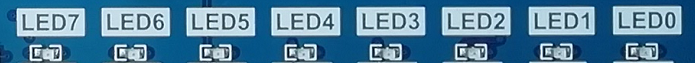

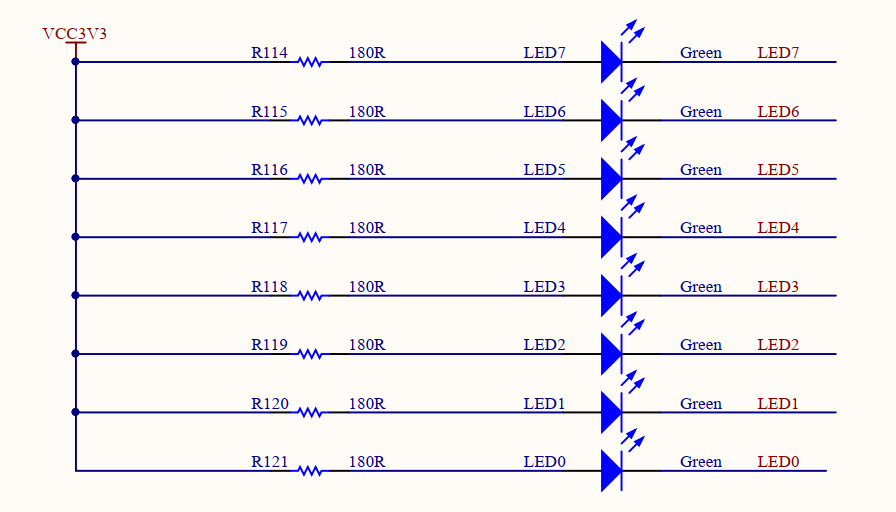

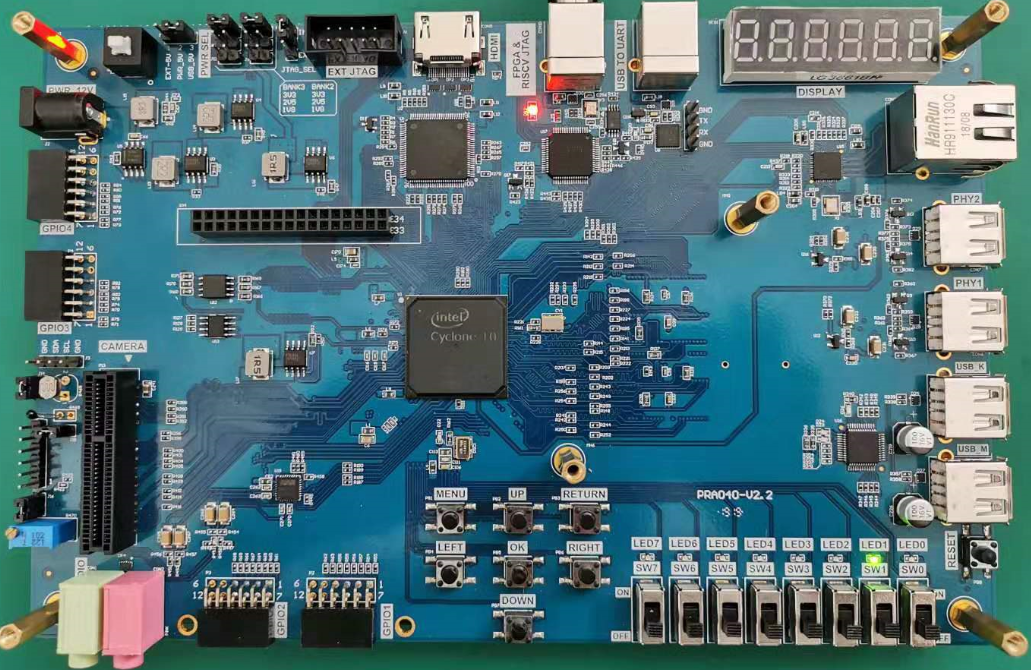

The physical picture of the onboard 8-bit LED is shown in Figure 1.2. The schematics of LED is shown in Figure 1.3. The LED module of this experiment board adopts 8 common anode LEDs, which are connected with Vcc 3.3V through 180 R resistors, and the cathodes are directly connected and controlled by the FPGA. When the FPGA outputs a low level of 0, a current flows through the LED, and it is turned on.

Figure 1.2 8-bit LED physical picture

Figure 1.3 Schematics of LED

1.3.3 Program Design

1.3.3.1 Start Program

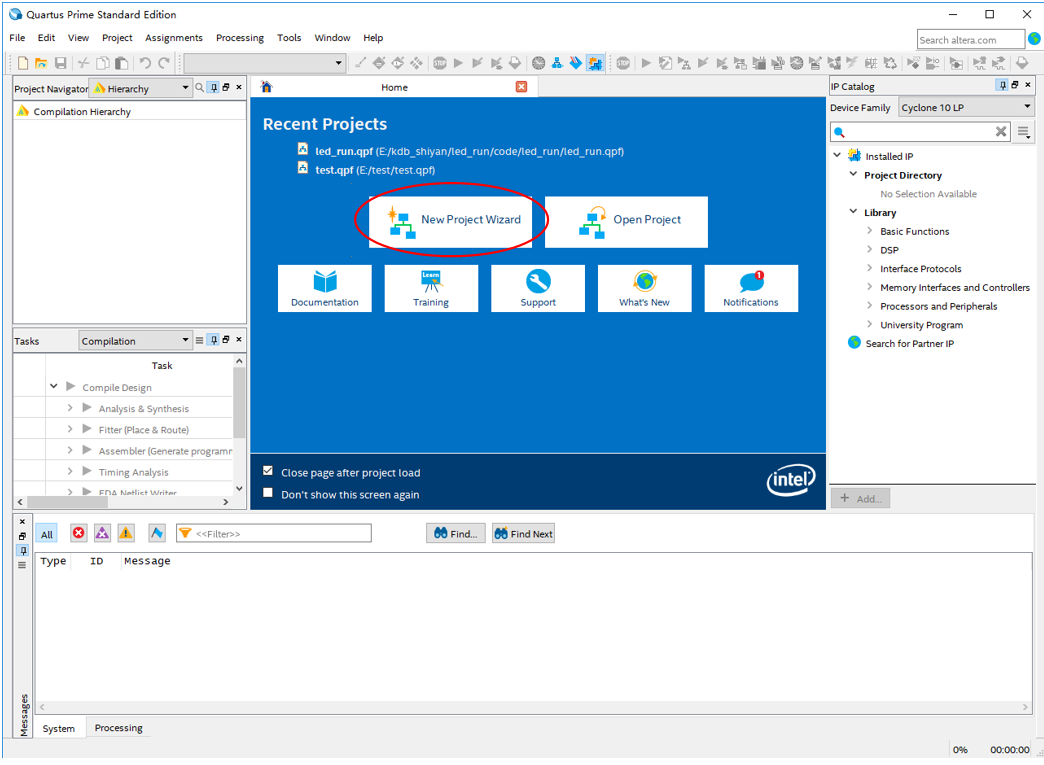

Before writing a program, let’s briefly introduce the development environment we use and how to create a project. Take Quartus II 18.1 as an example. The specific project establishment steps are shown in Figure 1.4 to 1.9.

- As shown in Figure 1.4, after opening Quartus, you can directly click New Project Wizard in the middle of the screen to create a new project. You can also click File to create a new project in the toolbar, or press Ctrl+N to create a new project.

Figure 1.4 The main Quartus II interface

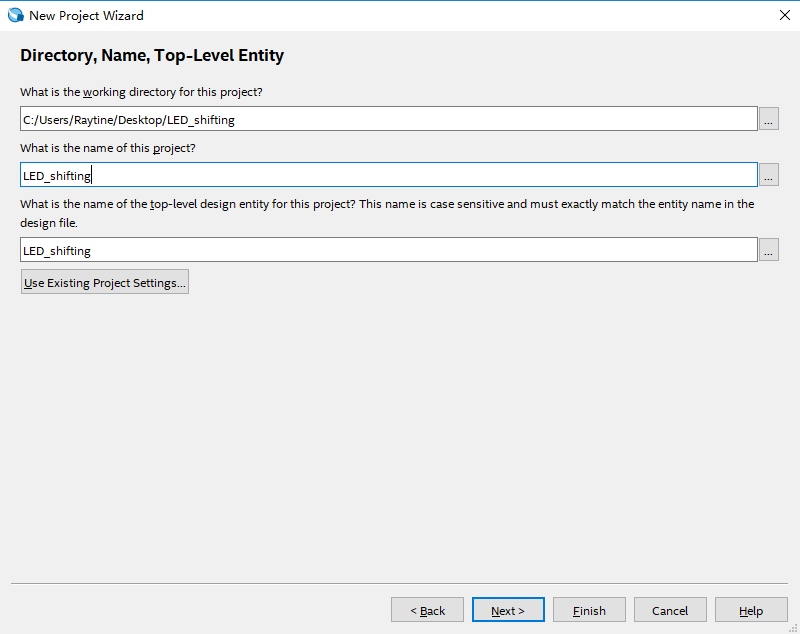

- As shown in Figure 1.5, select the correct project path. The project is named LED_shifting. It is recommended that the path is easy to find and convenient for later viewing and calling.

Figure 1.5 Name and define the path of the project file

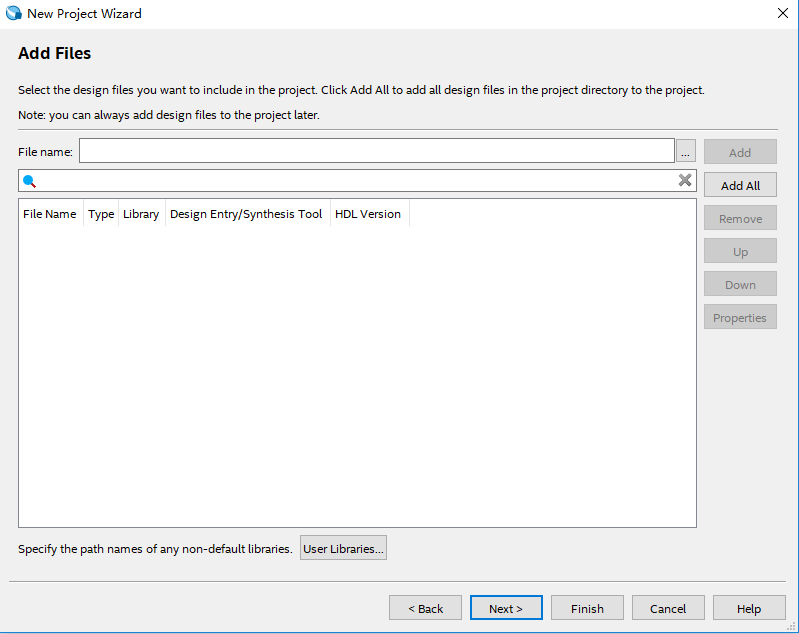

- As shown in Figure 1.6, you can directly add some files written in advance. Since it is a new project, click Next to perform the next step.

Figure 1.6 Add files

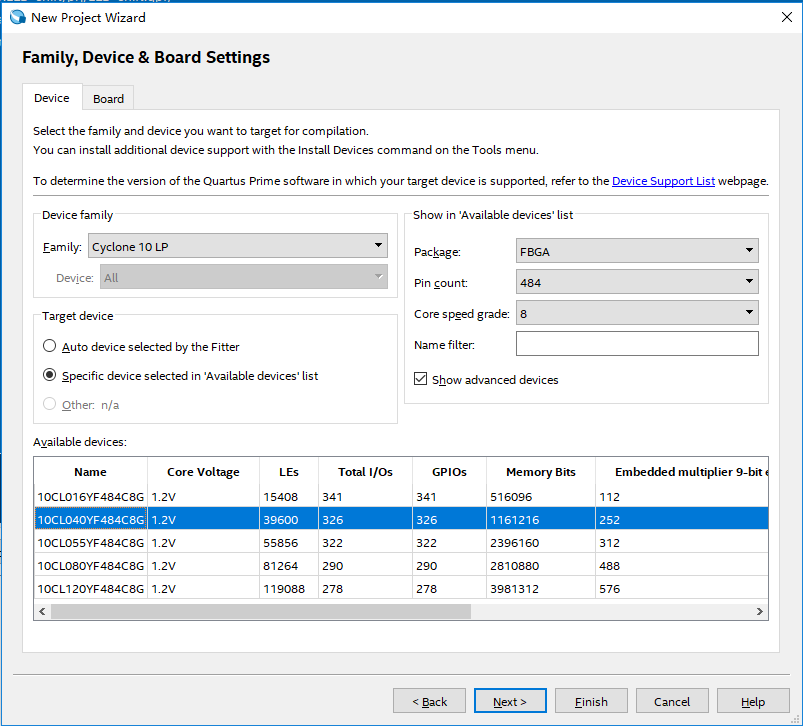

- As shown in Figure 1.7, select the correct FPGA chip model, the onboard chip model is 10CL040YF484C8G. Selecting Cyclone 10 LP in the Family, FBGA in the package, 484 in the Pin count, and 8 in the Core speed grage helps narrow down the selection and quickly find the target model.

Figure 1.7 Device selection

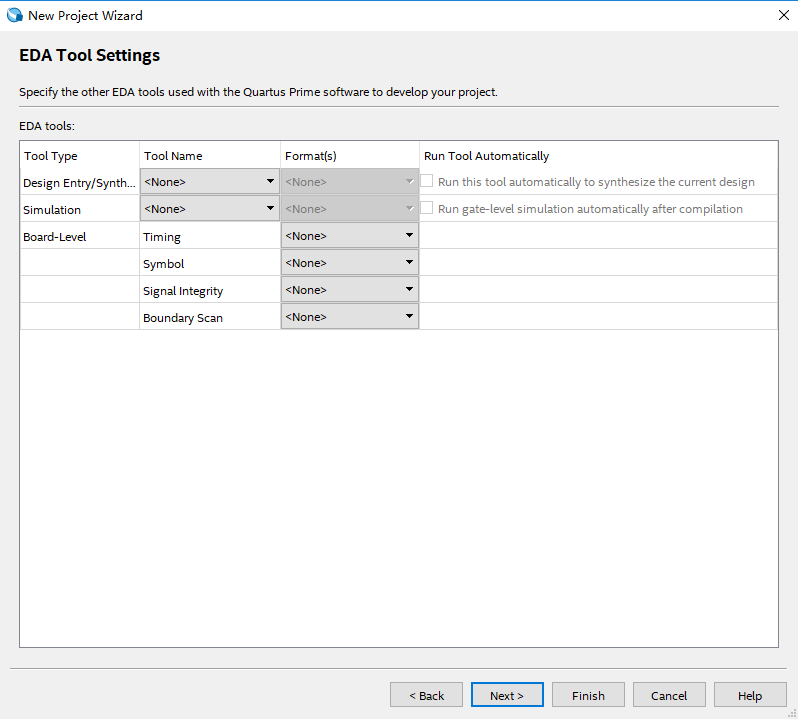

- As shown in Figure 1.8, select the EDA tool. Here use the EDA tool that comes with Quartus.

Figure 1.8 Selection of EDA tool

- Click Next to go to the next interface and select Finish to complete the project.

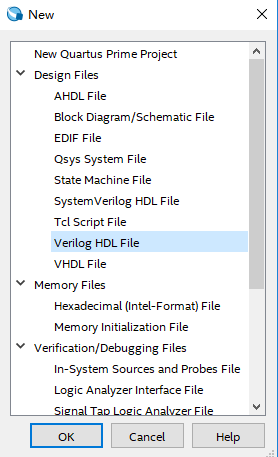

- Click File > New or use the shortcut key Ctrl+N to pop up the dialog box shown in Figure 1.9, create a program file (Verilog HDL File) to write code. Pay attention to the consistency of the program name and project name, and save it in the correct path (folder).

Figure 1.9 Create a new project file (LED_shifting.v)

Once the preparation is ready, start writing the program.

1.3.3.2 Program Introduction

The first step: the establishment of the main program framework (interface design)

|

The input signal of this experiment has 50 MHz system clock clk and reset signal rst_n. Output signal is led; 8 leds are defined by the multi-bit width form of led [7:0].

The second step: the call of IP Core, the establishment and use of PLL module

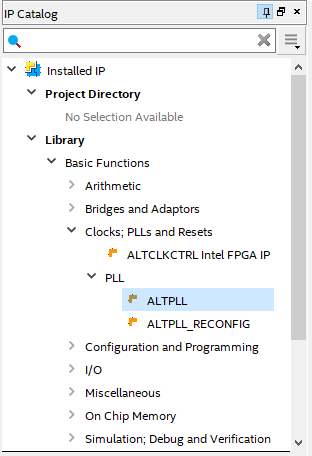

- As shown in Figure 1.10, find the ALTPLL in the IP catalog option bar on the right side of the main interface.

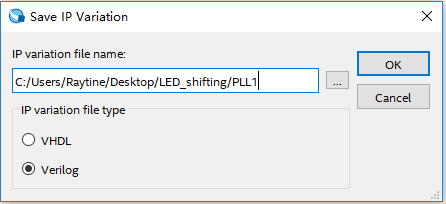

- As shown in Figure 1.11, double-click ALTPLL and enter the name of the PLL module in the pop-up dialog box. The name given here is PLL1. Note that the selection type is Verilog language type.

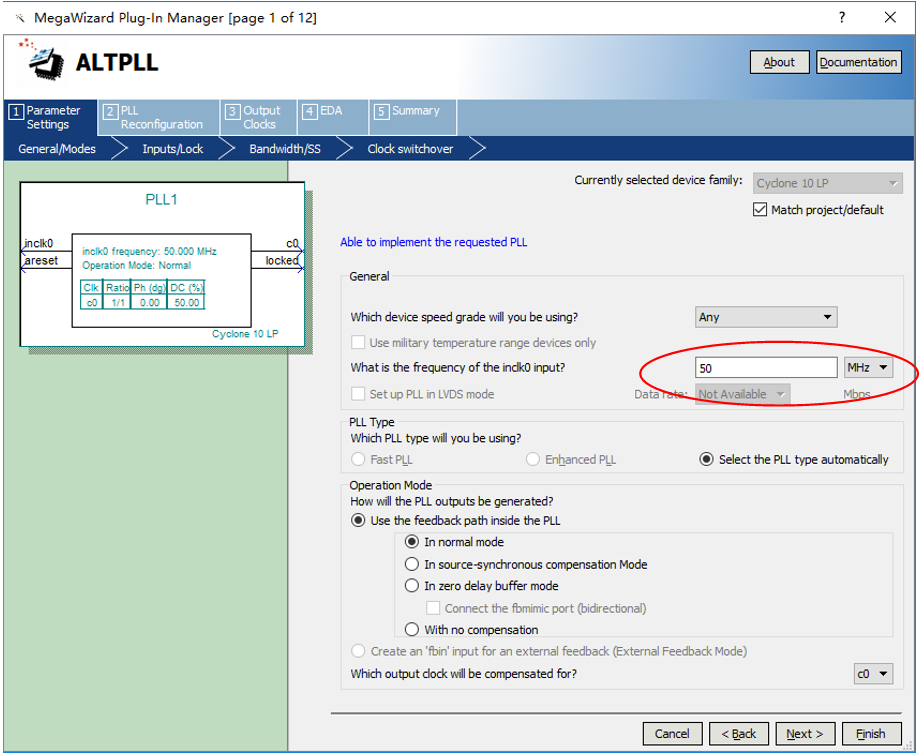

- As shown in Figure 1.12, after completing the previous step, enter the detailed setting interface. Inclk0 is the input clock of the PLL, provided by the development board, should be consistent with the system clock, set to 50MHz; PLL feedback path is set to normal mode. For advanced features involved, please read the reference; The output clock of the PLL compensation is C0; after the setting is completed, click Next to proceed to the next step.

Figure 1.10 IP Catalog

Figure 1.11 Name PLL

Figure 1.12 PLL setting1 (input clock setting)

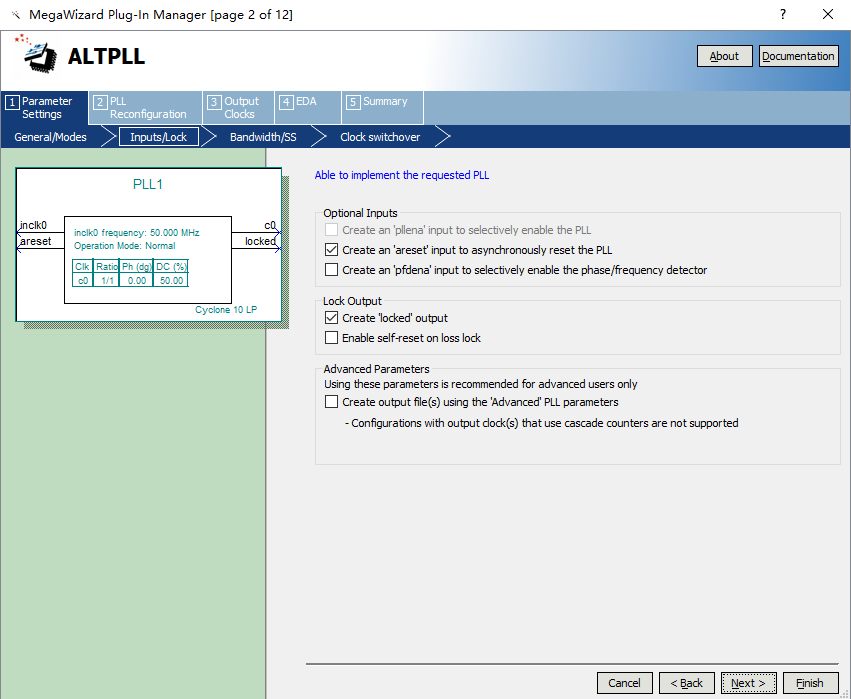

- As shown in Figure 1.13, it is the setting of PLL asynchronous reset (areset) control and capture lock (locked) status. This experiment can be selected according to the default mode in the figure.

Figure 1.13 PLL setting2

- The contents of the next three settings pages are executed by default.

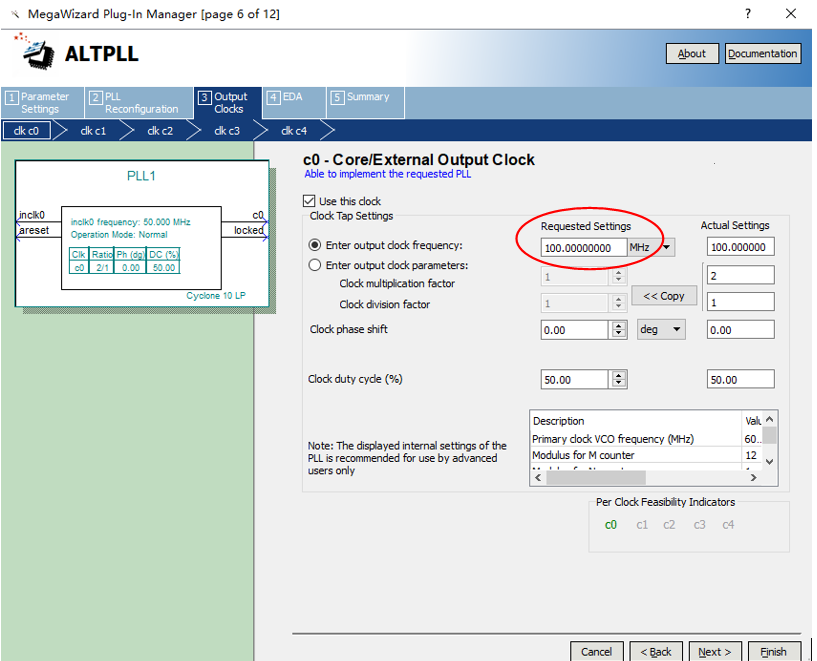

- As shown in Figure 1.14, it is the setting of the PLL output clock. It can output 5 different clocks clk c0~clk c4. This experiment only uses one, set clk c0, other defaults are not applicable. Set the output frequency to 100 MHz, the clock phase shift to 0, and the clock duty cycle to 50%.

Figure 1.14 PLL setting3 (output clock setting)

- Keep the EDA setting to be default.

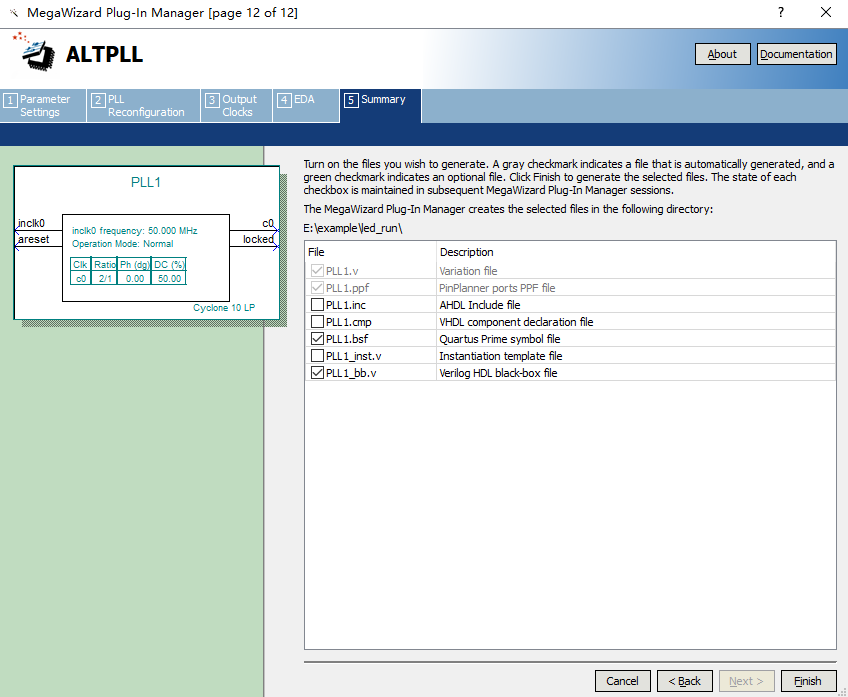

- As shown in Figure 1.15, the output file type setting selects *.bsf (used in the subsequent design of graphic symbols) files and *.v files. Others are set by default and click Finish to complete the settings.

Figure 1.15 PLL settings 4 (Output File Type Settings)

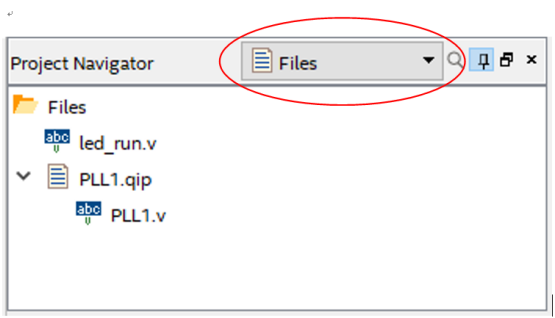

- As shown in Figure 1.16, select file in the Project Navigator type box of the project interface (the default is the project hierarchy).

Figure 1.16 PLL1.v file setting

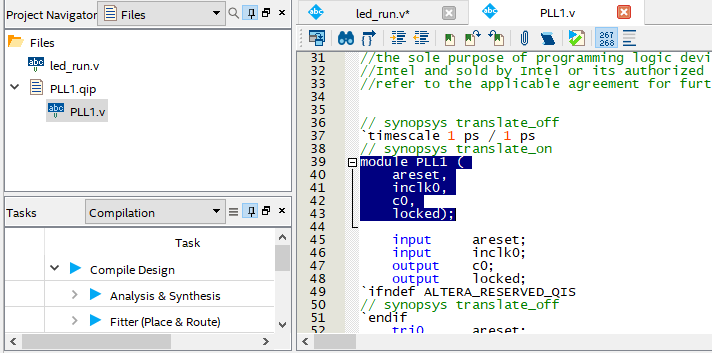

- As shown in Figure 1.17, click PLL1.v. The main window will display the contents of the PLL, find the module name and port list, copy it to the top level entity, and instantiate it.

Figure 1.17 PLL1.v file

When the system is powered on, the pll_locked signal has a value of 0 before the PLL is locked (stable operation), pll_locked is pulled high after the PLL is locked, and the clock signal sys_clk is output normally. The phase-locked loop is instantiated as follows:

|

- Sys_rst is used as the reset signal of the frequency division part, and ext_rst is used as the reset signal of the part of the running LED. Under the drive of the clock sys_clk, it is synchronously reset by the primary register.

|

The third step: the design of the frequency divider

We use the 100 MHz clock output by PLL as the system clock. The experiment requires the blinking speed of the running light to be 1 second. The design is firstly obtained 1us by microsecond frequency division, then dividing into milliseconds to get 1ms, and finally get 1s clock through second frequency division.

- Microsecond frequency division

|

The 100 MHz clock has a period of 10ns, and 1us requires 100 clock cycles, that is, 100 10ns. Therefore, a microsecond counter us_cnt [6:0] and a microsecond pulse signal us_f are defined. The counter is cleared at reset. On each rising edge of the clock, the counter is incremented by one. When the counter is equal to 99, the period of 1us elapses, and the microsecond pulse signal us_f is pulled high. Thus, every 1us, this module will generate a pulse signal.

- Millisecond frequency divider

Similarly, 1ms is equal to 1000 1us, so a millisecond counter ms_cnt [9:0] and a microsecond pulse signal ms_f are defined.

|

- Second frequency divider

Similarly, 1s is equal to 1000 1ms, so a second counter s_cnt [9:0] and one second pulse signal s_f are defined. When the three counters are simultaneously full, the time passes for 1 s and the second pulse signal is issued.

|

The fourth step: the design of the shifting LED

When resetting, 8 LEDs are all on, so the output led is 8’h00. The LEDs need to blink one by one, so the lowest LED is lit first. At this time, the led value is 8’b1111_1110. When the second pulse signal arrives, the next LED is illuminated, and the value of led is 8’b1111_1101.It can be seen that as long as the high level of “0” is shifted to the left, it can be realized by bit splicing, that is, led <= {led[6:0], led[7]}.

|

1.4 Experiment Verification

1.4.1 Some Preparation Before Verification

Figure 1.18 Introduction to some functions

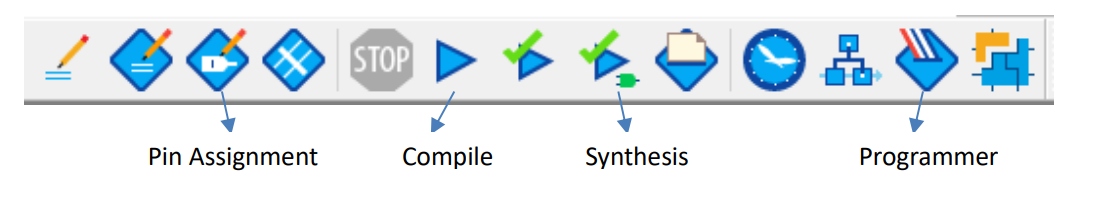

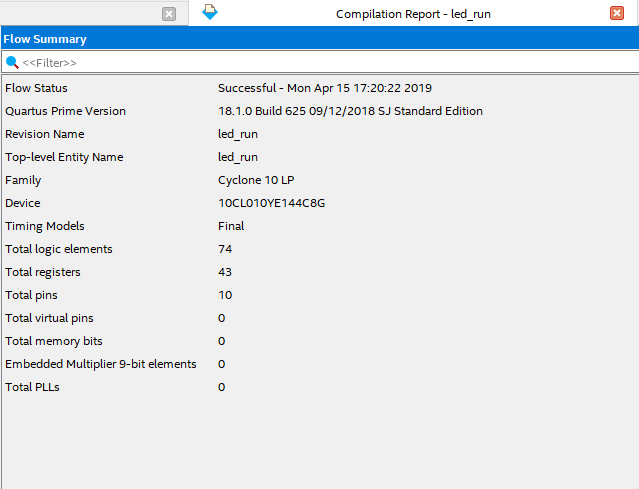

As shown in Figure 1.18, after the program is written, analysis and synthesis is required to check for errors. Click the synthesis icon to complete, or use the shortcut key Ctrl+K, the pin assignment is to bind each signal to the FPGA pin, the compilation is to generate the programming file for the development board and check the error again. Click the programmer icon, and follow the instructions to program the development board. Click on the synthesis icon, Quartus will automatically generate a report, as shown in Figure 1.19. The details of the report are not described here.

Figure 1.19 Compilation report

Check and modify to no error before board verification. Do the pin assignment before actually programming the board.

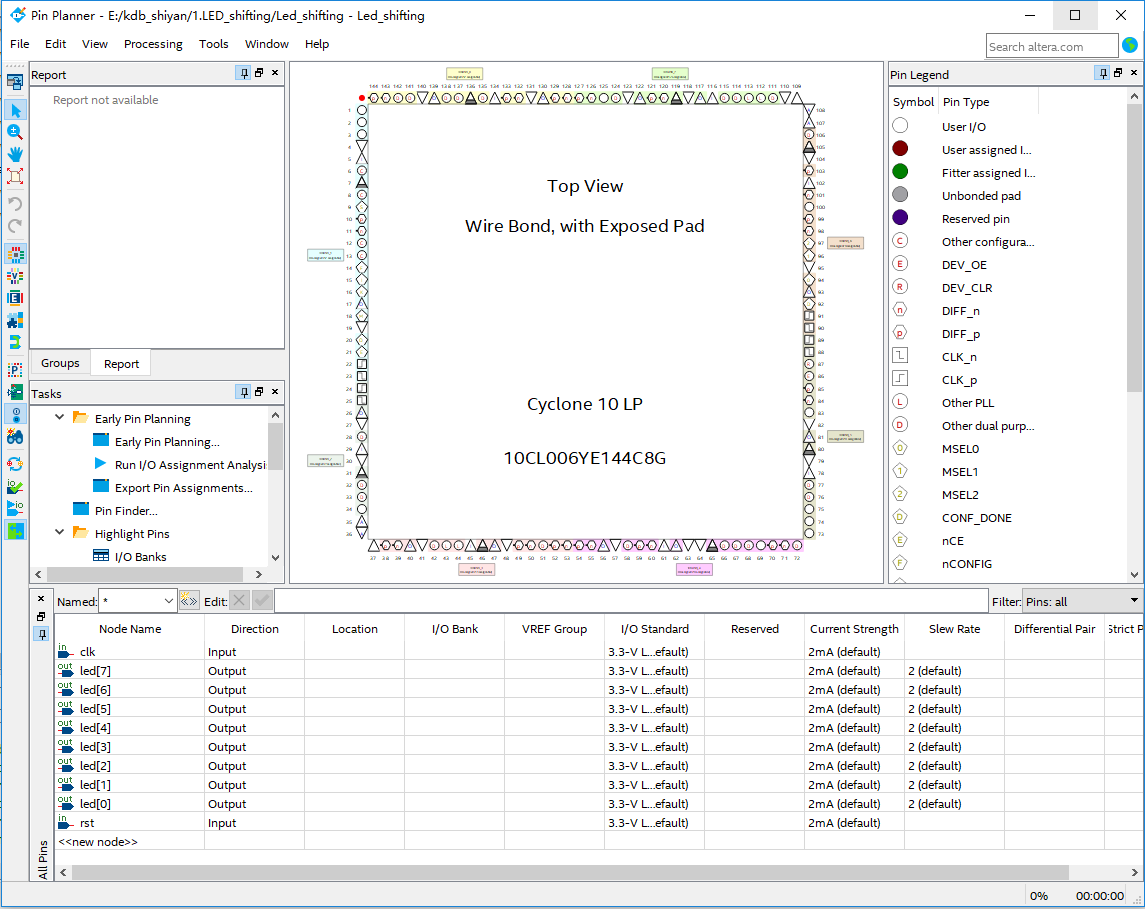

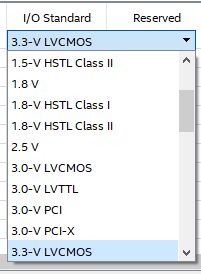

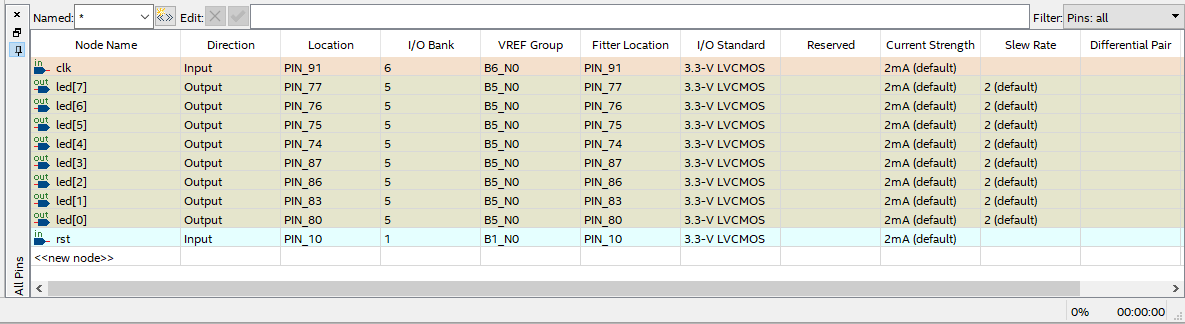

Table 1.1 Pin mapping

Click the pin assignment icon to open the pin assignment window, as shown in Figure 1.20. Double-click the location column corresponding to each pin, directly enter the pin number, or click the drop-down button to find the corresponding pin, but the latter is relatively slow. It should be noted that the I/O standard column in Figure 1.21, the content shown is the voltage standard of each I/O port, determined by the BANK voltage in the schematics and the design requirements. In this experiment, the I/O voltage should be selected as 3.3V. Double-click the I/O standard column and click the pull-down button, as shown in Figure 1.22, select the right voltage standard. The default voltage standard can be set in advance when selecting the chip model. Click Device and Pin Options -> Voltage -> Default I/O standard in Figure 1.7 to set it.

The pin assignment is complete, as shown in Figure 1.22. Then click on the compilation. After completion, program the development board.

Figure 1.20 Pin assignment window

Figure 1.21 I/O voltage selection

Figure 1.22 Pin assignment overview

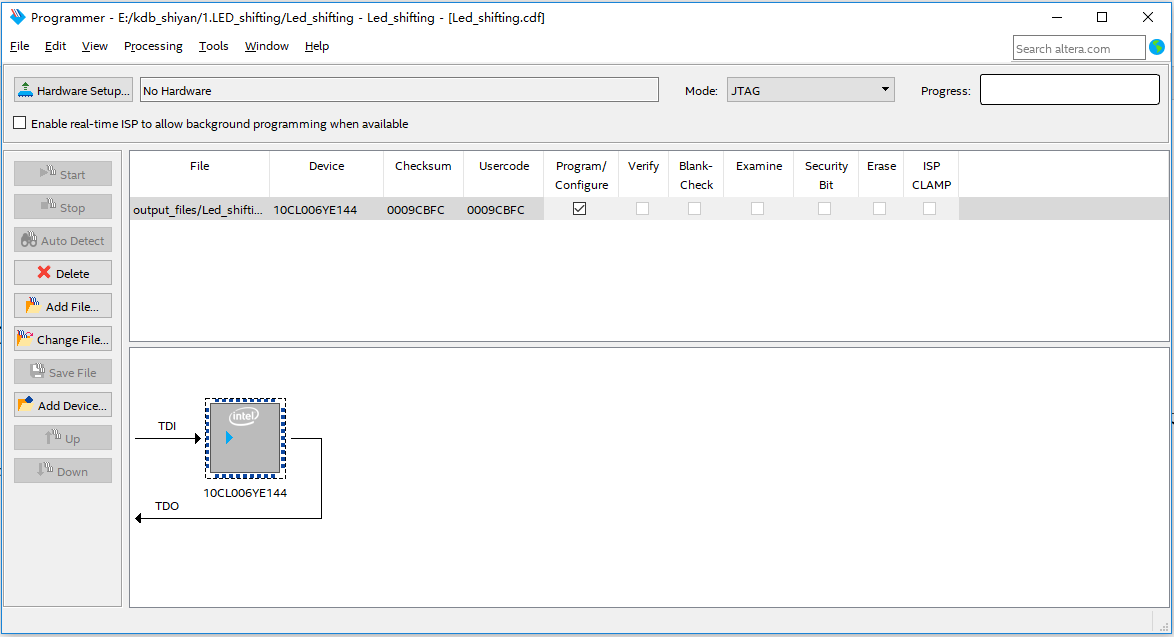

1.4.2 Program the Board

Before programming the board, some settings should be made for the Quartus. For details, please refer to the “Intel FPGA Download Cable II User Guide” for reference. After the settings according to the instructions, click programmer icon to open the download window, as shown in Figure 1.23.

Figure 1.23 Programmer window

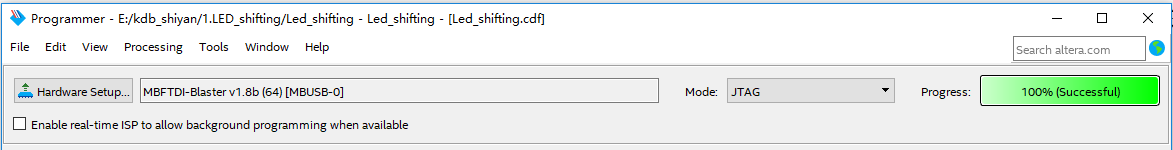

After connecting the development board to the host computer, click on Hardware Setup and select development board, as shown in Figure 1.24.

Figure 1.24 Hardwrae setup

Click Start to start the download, as shown in Figure 1.25, Progress shows 100% (Successful), that is, the download is completed.

Figure 1.25 Program successfully

See Figure 1.26, the LEDs is lit from low to high and the interval is one second.

Figure 1.26 Experiment result