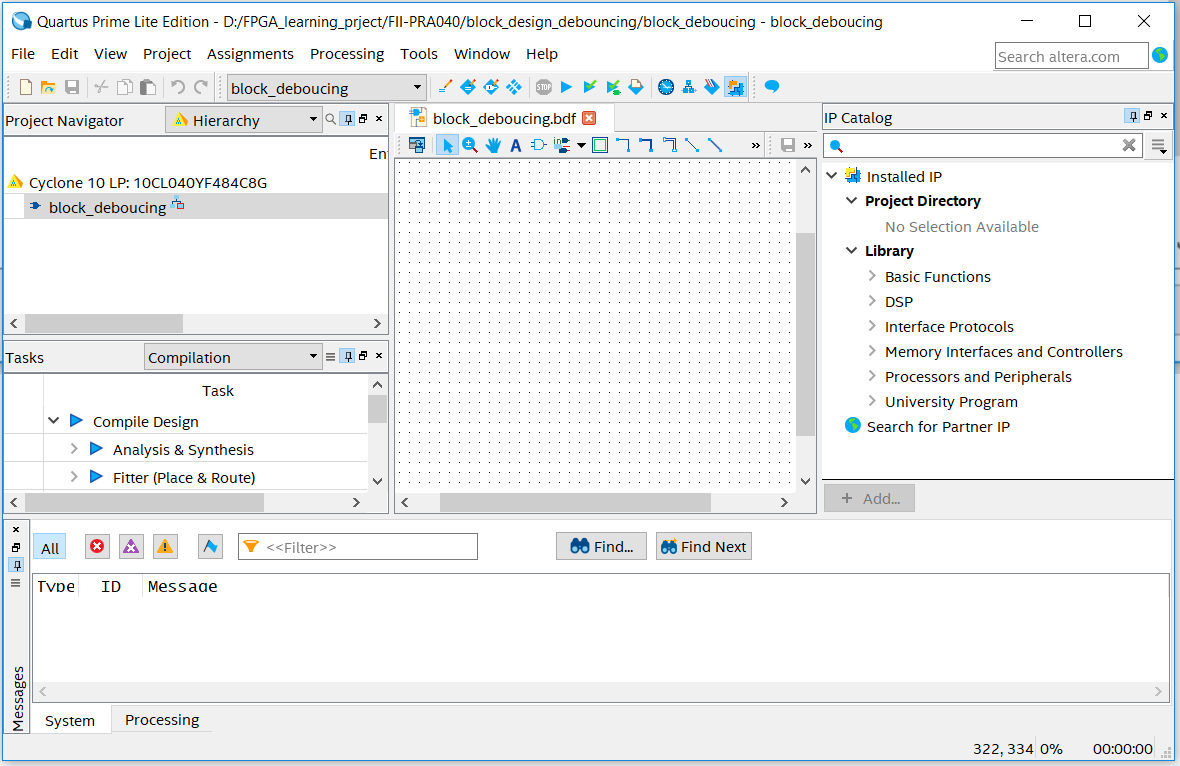

Ubuntu Network Connections Guide in FPGA Board Development Environment

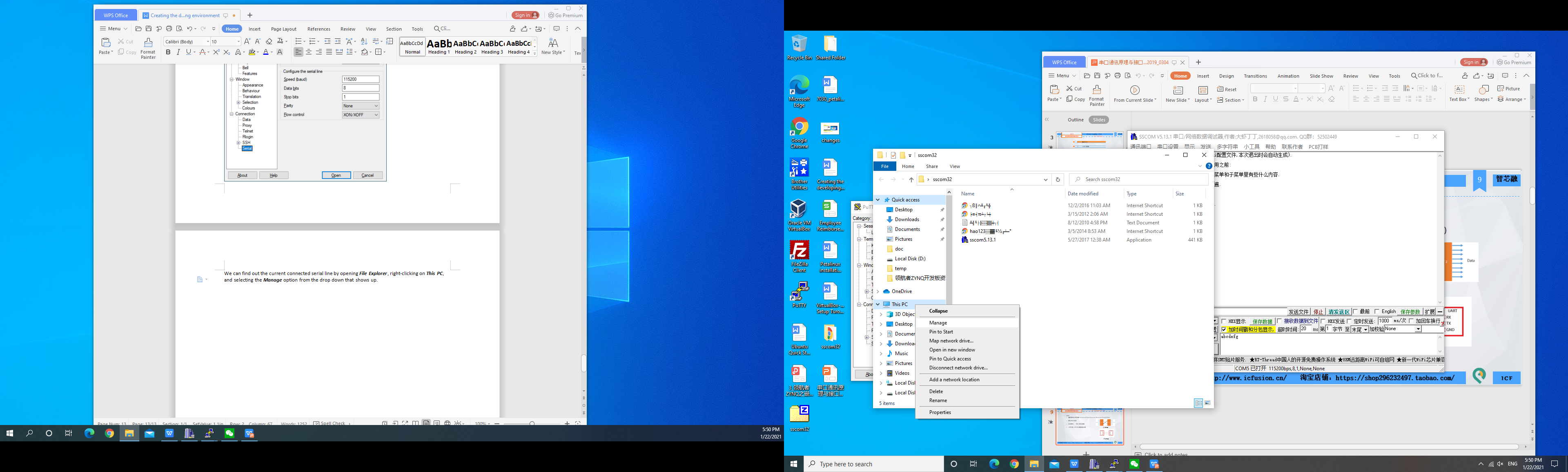

Ubuntu Network Connections Guide Table of Contents Section 1: Exchanging Files Between Ubuntu and Windows 3 Setting up FTP in Ubuntu 3 Setting up the FTP Client in Windows 4 Setting up FileZilla and Transferring Files 5 Section 2: Creating a tftp Server in Ubuntu 9 Using NFS and SSH in Ubuntu 10 Turing on NFS 10 Turning on SSH 11 Installing and Using PuTTY 12 Installing PuTTY 12 Using PuTTY 14 Section 1: Exchanging Files Between Ubuntu and Windows *In order to follow along to this tutorial, you…

Read More