BCD decoder, Display design of hexadecimal to 7 segment display decoders, Achieve digital clock display – zynq xc7z030 board – FII-PE7030 Experiment 3 – Segment Display Digital Clock Experiment

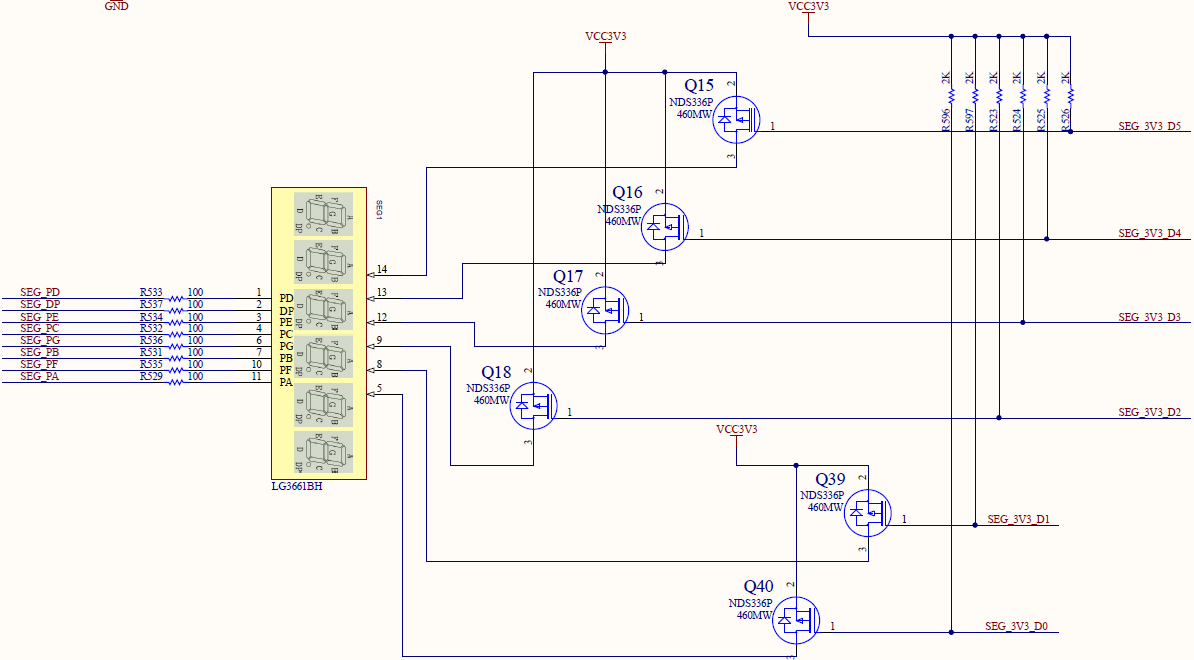

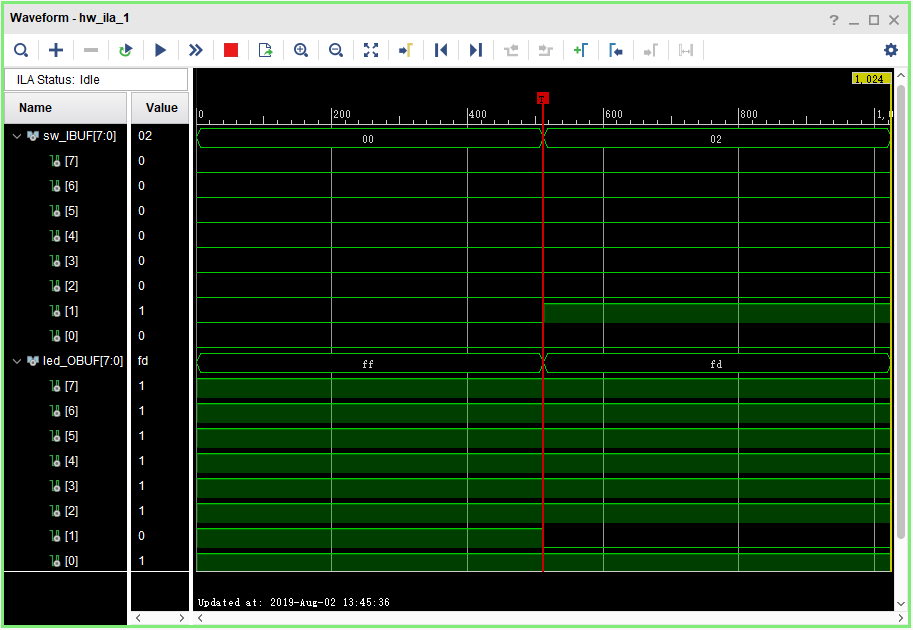

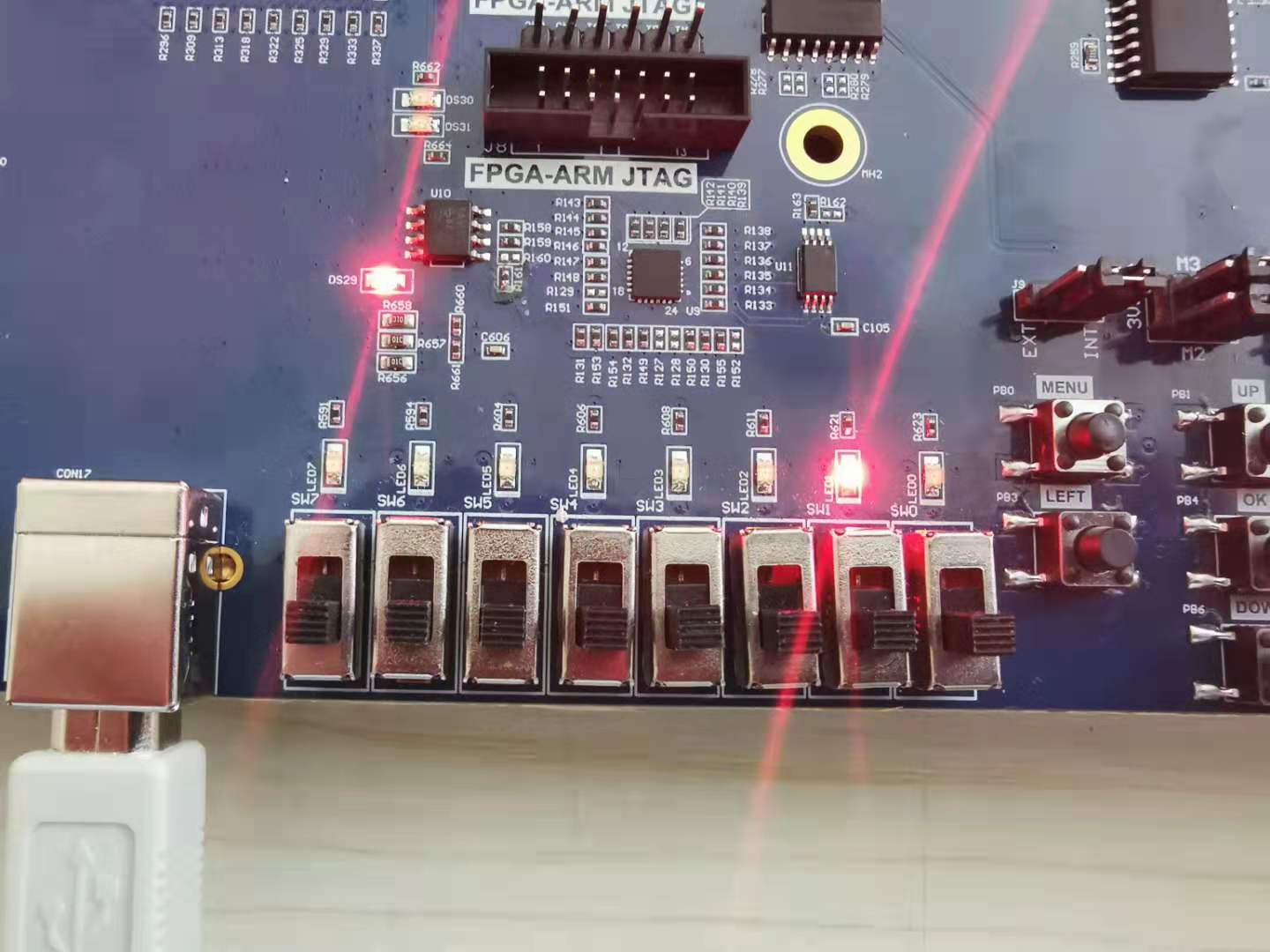

3.1 Experiment Objective Review the contents of experiment 1 and experiment 2, master the configuration of PLL, the design of frequency divider, the principle of schematics and the pin assignment of FPGA. Familiar with the design of Verilog’s tree hierarchy Study BCD decoder Display design of hexadecimal to 7 segment display decoders Achieve digital clock display 3.2 Experiment Implement The display decoder has two lower digits to display seconds, the middle two digits to display minutes, and the highest two digits to display hours. Separate the seconds, minutes, and hours…

Read More