Learn to Analyze the Captured Signals, Practice the Use of SignalTap Logic Analyzer in Quartus – SignalTap – Altera Risc-V Board PRA040 Experimental 2

Experiment 2 SignalTap

2.1 Experiment Objective

- Continue to practice the use of the development board hardware;

- Practice the use of SignalTap Logic Analyzer in Quartus;

- Learn to analyze the captured signals.

2.2 Experiment Implement

- Use switches to control the LED light on and off

- Capture and analyze the switching signals on the development board through the use of SignalTap.

2.3 Experiment

2.3.1 Introduction of DIP Switches and SignalTap

- Introduction of switches

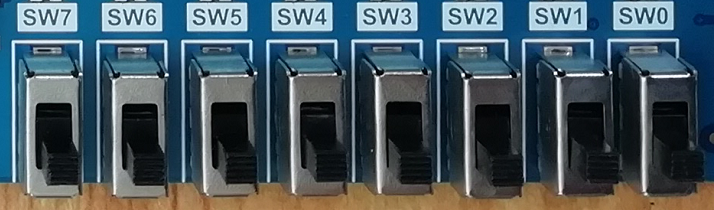

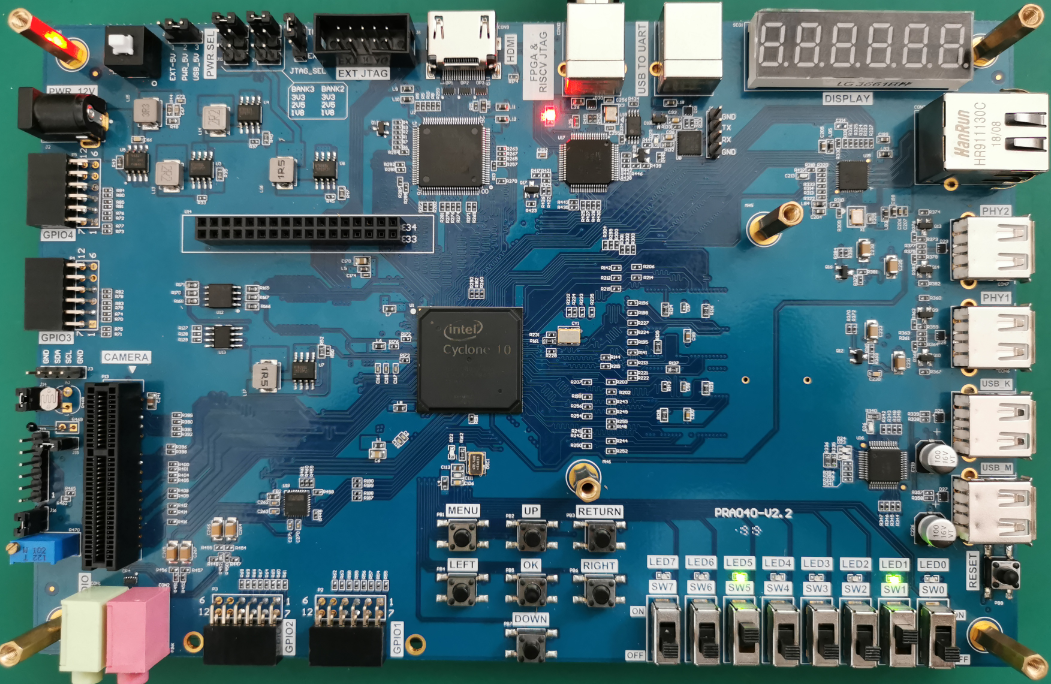

The on-board switch is 8 DIP switches, as shown in Figure 2.1. The switch is used to switch the circuit by turning the switch handle.

Figure 2.1 Switch physical picture

- Introduction of SignalTap

SignalTap uses embedded logic analyzers to send signal data to SignalTap for real-time analysis of internal node signals and I/O pins when the system is operating normally.

2.3.2 Hardware Design

The schematics of the switch is shown in Figure 2.2. Port 2 of the 8 switches is connected to VCC, and port 3 is connected to the FPGA. Therefore, when the switch is toggled to port 3, the switch is turned on and input to the FPGA a high level signal.

Figure 2.2 Schematics of the switches

2.3.3 Program Design

The first step: the establishment of the main program framework (interface design)

|

The experimental input signals have a system clock clk with frequency of 50 MHz, an high effective 8-bit switch sw, and an output 8-bit led.

The second step: realize the switch control LED

|

When the reset signal is valid, all 8 LEDs are off. After the reset is completed, the LED light is turned on and off by the switch.

2.4 Use and Verification of SignalTap Logic Analyzer

The first step: pin assignment

Pin assignments are shown in Table 2.1. Compile when pin assignment is finished.

Table 2.1 Pin Mapping

| Signal Name | Network Label | FPGA Pin | Port Description |

| clk | C10_50M | G21 | Input clock |

| SW[7] | PB7 | W6 | Switch 7 |

| SW[6] | PB6 | Y8 | Switch 6 |

| SW[5] | PB5 | W8 | Switch 5 |

| SW[4] | PB4 | V9 | Switch 4 |

| SW[3] | PB3 | V10 | Switch 3 |

| SW[2] | PB2 | U10 | Switch 2 |

| SW[1] | PB1 | V11 | Switch 1 |

| SW[0] | PB0 | U11 | Switch 0 |

| led[7] | LED7 | F2 | LED 7 |

| led[6] | LED6 | F1 | LED 6 |

| led[5] | LED5 | G5 | LED 5 |

| led[4] | LED4 | H7 | LED 4 |

| led[3] | LED3 | H6 | LED 3 |

| led[2] | LED2 | H5 | LED 2 |

| led[1] | LED1 | J6 | LED 1 |

| led[0] | LED0 | J5 | LED 0 |

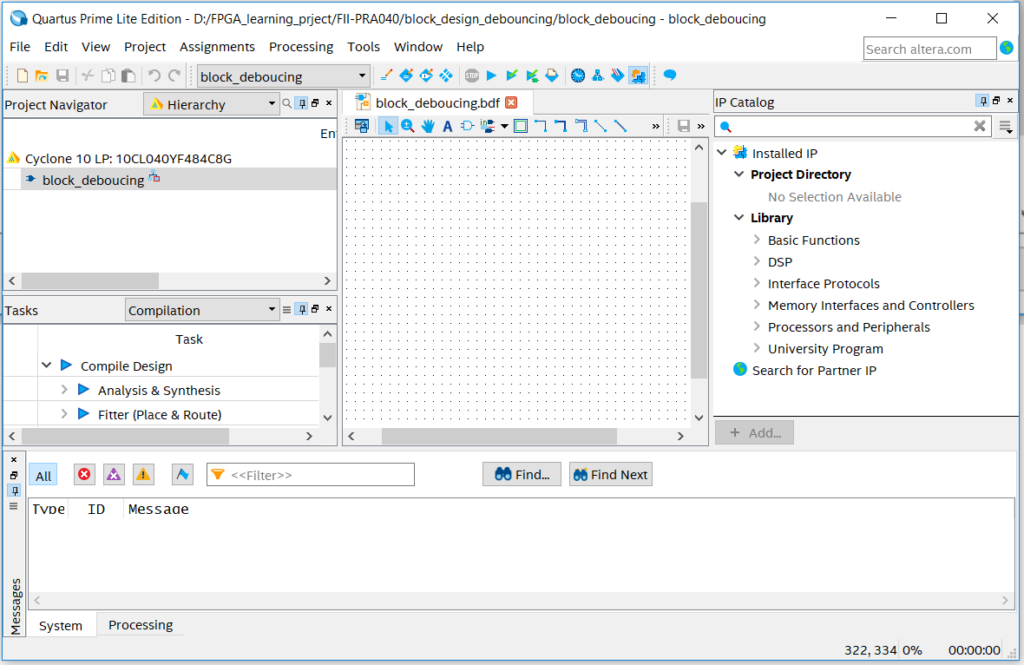

Step 2: SignalTap II startup and basic settings

Menu Tools -> SignalTap II logic Analyzer,

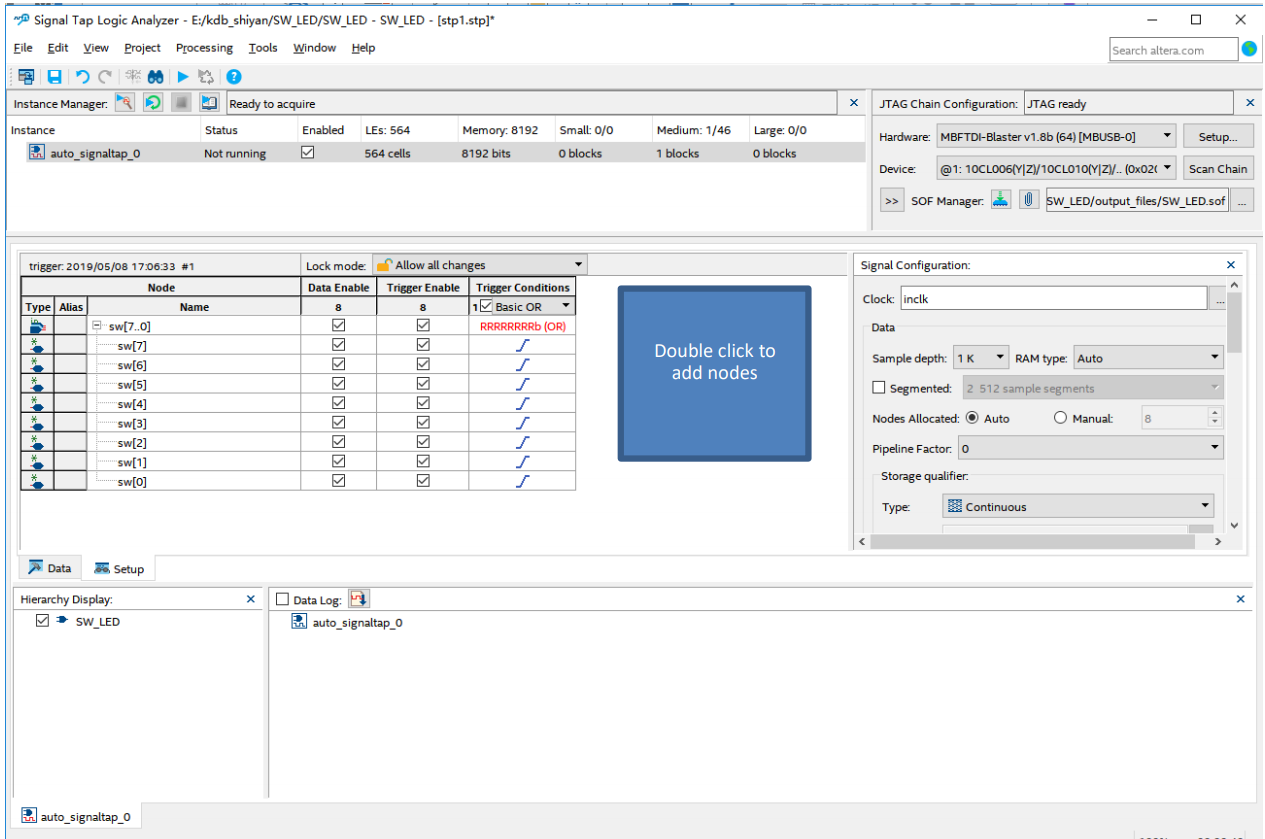

- In Figure 2.3, set the data under Signal Configuration

- Set the JTAG configuration and click on Setup to set the downloader.

- Set the device type by clicking Scan Chain

- Set up SOF Manager: set as *.SOF that is just compiled and generated before

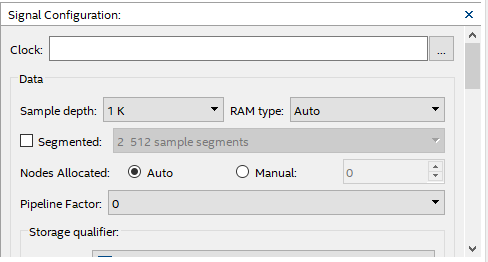

- Clock and storage depth settings are shown in Figure 2.4.

Click the position shown in Figure 2.4 to add the clock. As shown in Figure 2.5, in the Clock Settings dialog box: Filter select SignalTap: pre-synthesis -> List, select the desired clock signal, select c0 in PLL1: PLL1_INST, move to the box on the right.

Other settings can be set as shown in Figure 2.2. (for advanced use of SignalTap II, please read the reference)

Figure 2.3 SignalTap setting interface

Figure 2.4 Clock signal and the sample depth

Figure 2.5 Clock signal selection dialogue

Step 3: Add observation signal

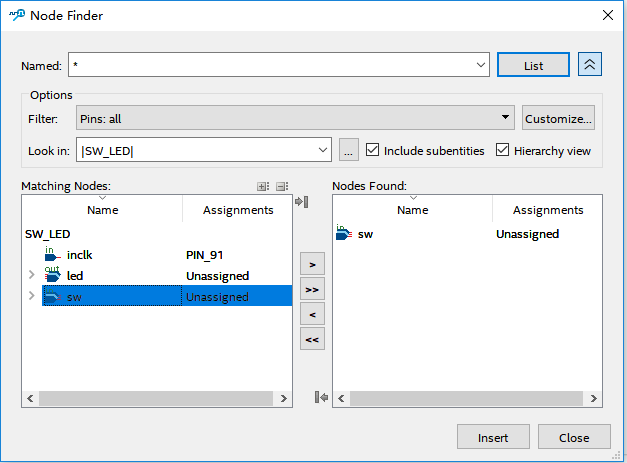

Figure 2.6 Adding interface for the observe signals

As shown in Figure 2.3, double-click the blank to add the observation signal. Adding interface is shown in Figure 2.6. Select the signal you want to observe on the left side, add it to the right side, click Insert. Save it and recompile.

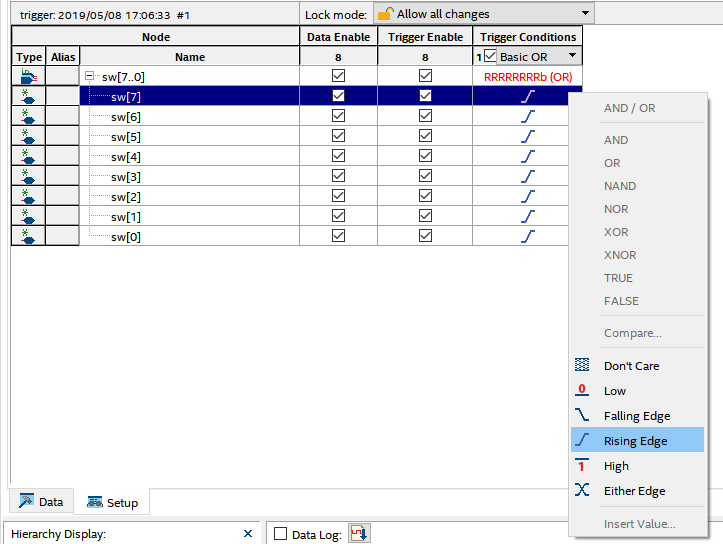

Step 4: Settings of observe signals

For the signal to be observed, whether it is a rising edge trigger, a falling edge trigger, or not care, etc., need to be manually adjusted, as shown in Figure 2.7.

Figure 2.7 Trigger signal setting

Step 5: Observe the results

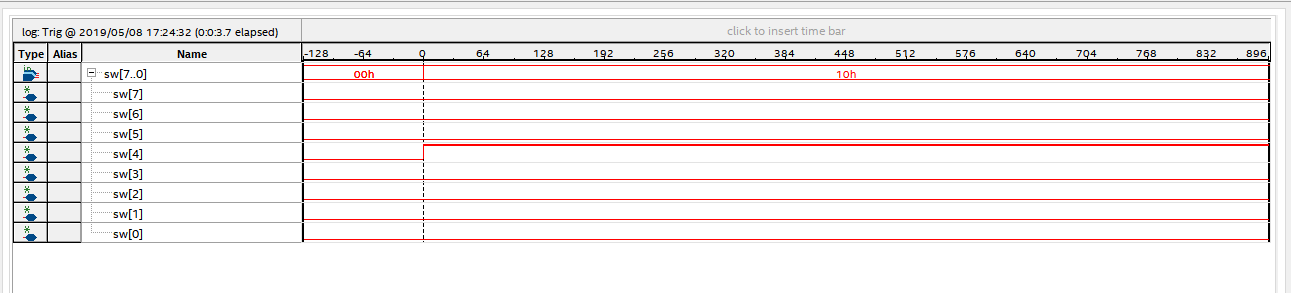

As shown in Figure 2.7, click Run Analysis to observe the output of SignalTap.

Figure 2.8 Test result

After the switch sw[4] is turned on, its signal is high, and the corresponding LED will be lit. Modify the Trigger condition, test the output results under different Trigger conditions, analyze and summarize.

The experimental phenomenon is shown in Figure 2.9. When the switches sw5 and sw1 are on, the corresponding LED5 and LED1 are illuminated, and the other LEDs remain off.

Figure 2.9 Experiment result