Combined With the BCD_Counter Project to Achieve the Display of the Digital Clock, Master the Design Method of Graphics From Top to Bottom – Block/SCH – Altera Risc-V Board PRA040 Experimental 4

Experiment 4 Block/SCH

4.1 Experiment Objective

- Review building new FPGA projects in Quartus, device selection, PLL creation, PLL frequency setting, Verilog’s tree hierarchy design, and the use of SignalTap II

- Master the design method of graphics from top to bottom

- Combined with the BCD_counter project to achieve the display of the digital clock

- Observe the experimental results

4.2 Experiment Implement

Use schematics design to build the project.

4.3 Experiment

This experiment is mainly to master another design method. The other design contents are basically the same as the experiment 3 and will not be introduced in detail. The modular design method is introduced below.

- New project: File -> New Project Wizard…

Project name: block_counter

Select device (10CL040YF484C8G)

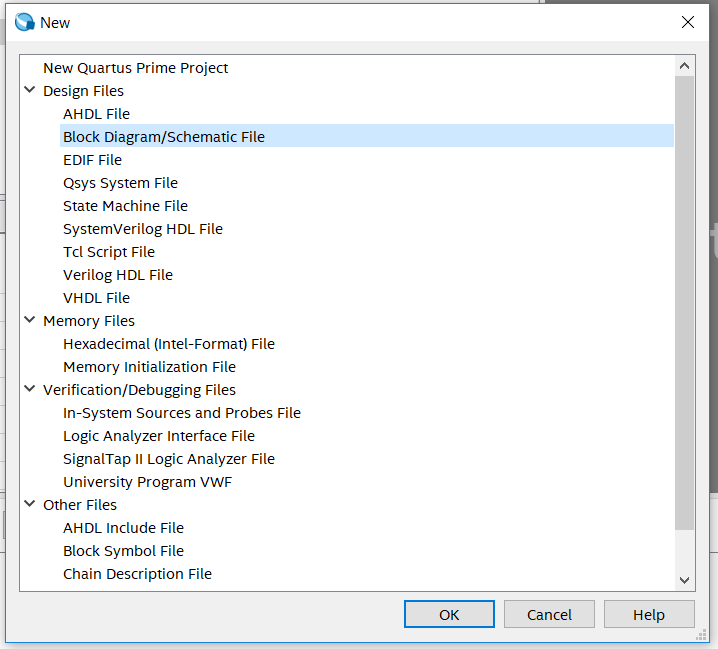

- Create new file; File -> New, select Block Diagram/Schematic File. See Figure 4.1.

Figure 4.1 New file

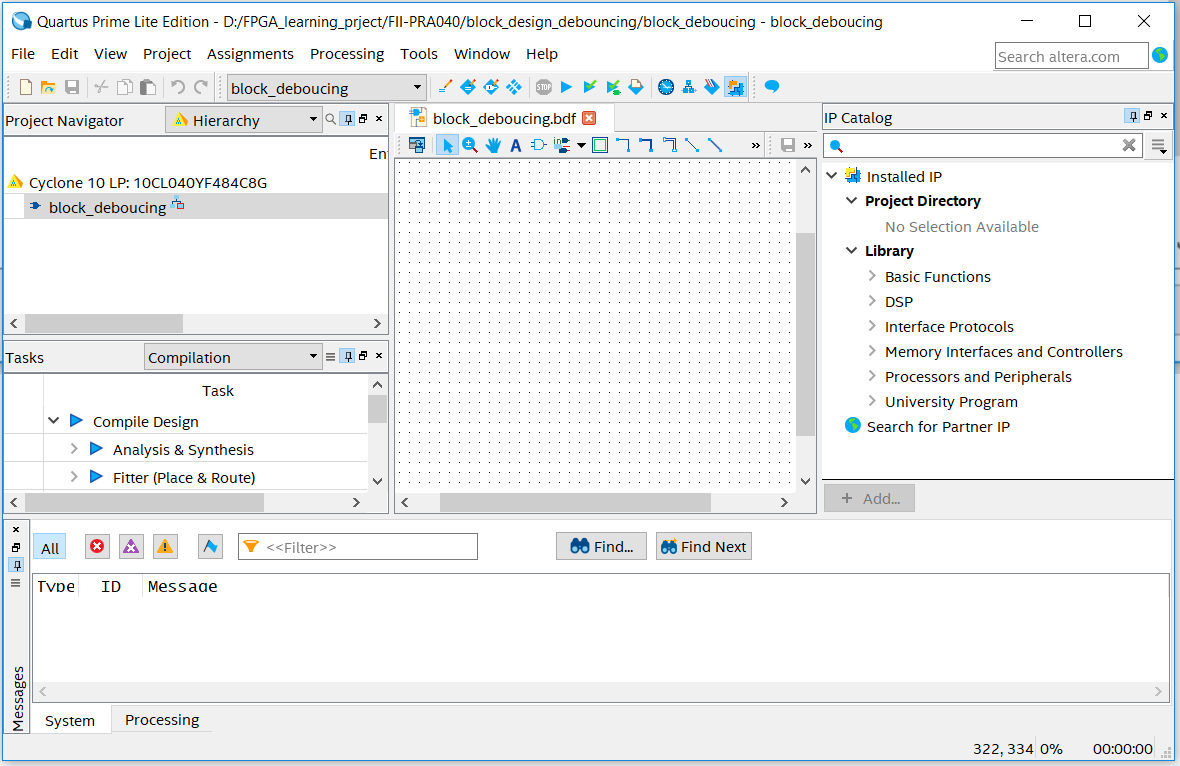

- See Figure 4.2, the middle part is the graphic design area, which can be used for Block/SCH design.

- Save the file as block_counter.bdf

- Double-click the blank space in the graphic design area to add a symbol

Figure 4.2 Graph design interface

- Graphic editing

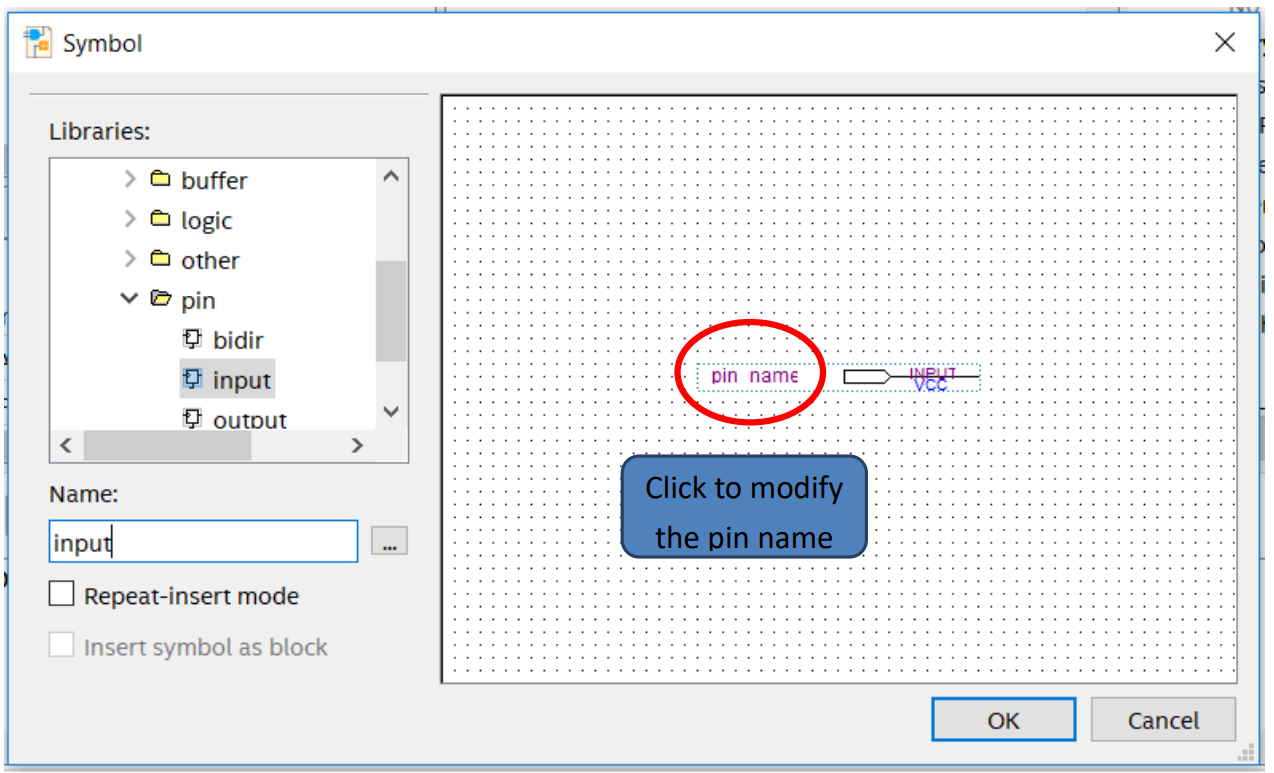

Double-click on the graphic design area to select the appropriate library and device in the libraries

Figure 4.3 Input symbol

- Add input, output, and modify their names

- Add a custom symbol

- Create a new block/sch file and save it as PLL_sys.bdf

- Add PLL IP, refer to experiment 1

- Select the generated file to include the PLL1.bsf file

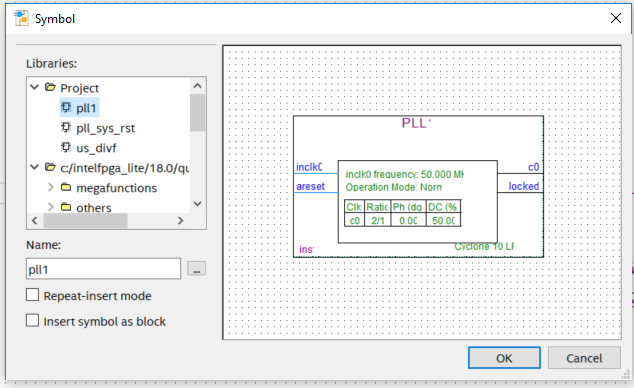

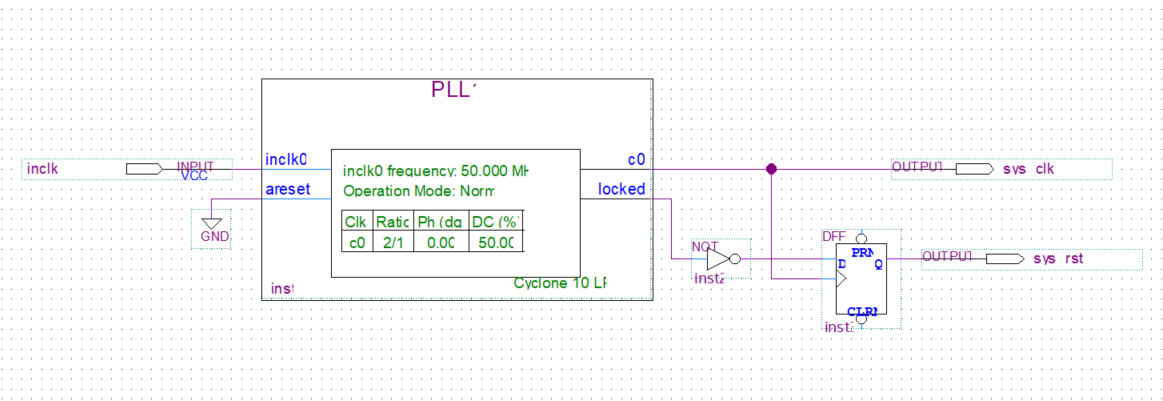

- Double-click in the blank area of the PLL_sys.bdf file to select the PLL1 symbol just generated and add it to the file, as shown in Figure 4.4.

Figure 4.4 Invoke the symbols generated in the IP catalog in the graphical editing interface

- Continue to add other symbols, input, output, dff, GND, etc. and connect them, as shown in Figure 4.5.

Figure 4.5 Connect the device

- Recreate the newly created file symbol for graphic editing to use in subsequent design

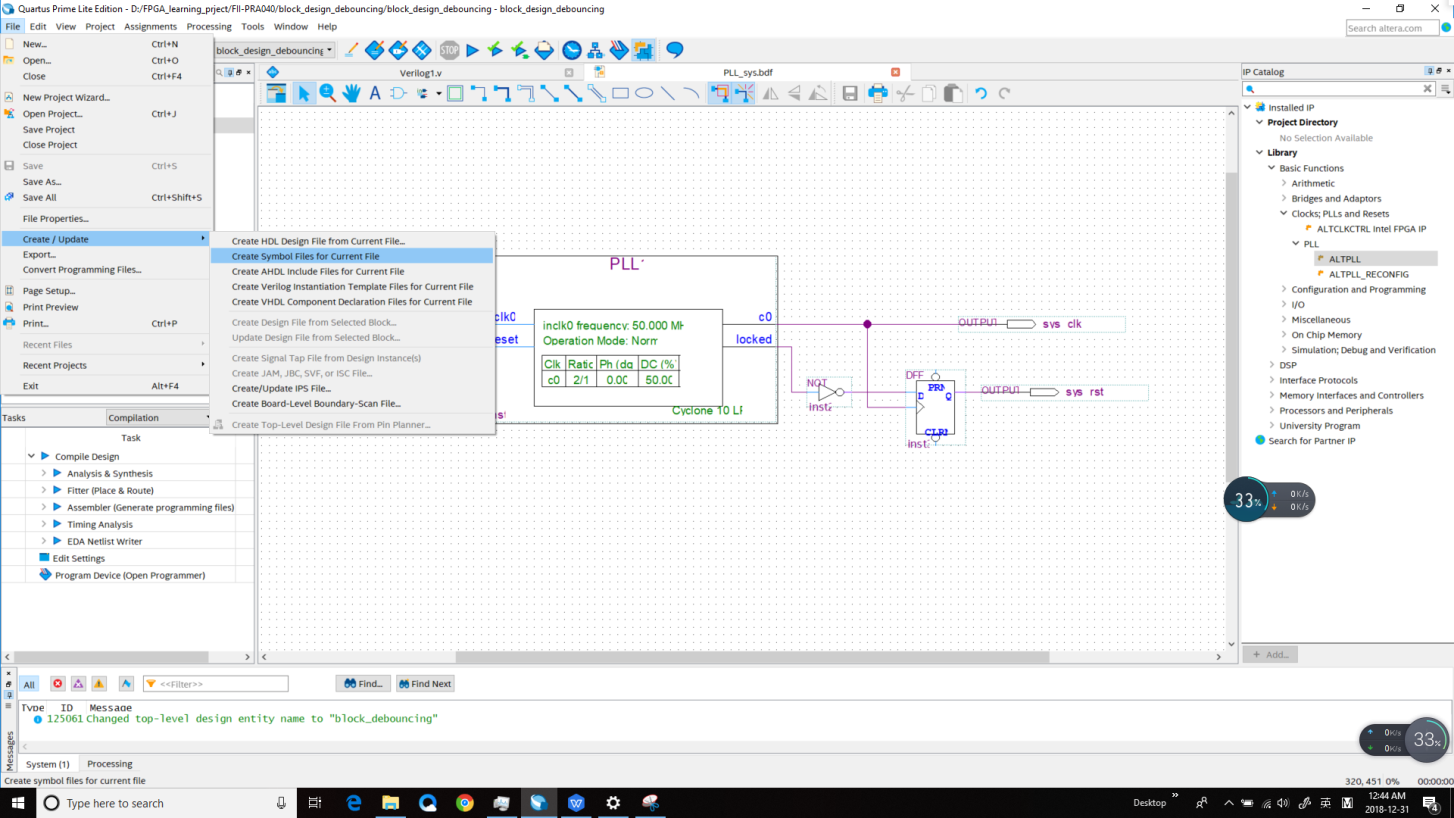

- File -> Create/Update -> Create Symbol file for Current File. See Figure 4.6.

- Generate PLL_sys.bsf

Figure 4.6 Creating a symbol file for the current file (symbol file *.bsf)

- Create a frequency division module

- Create a new verilog file div_us for the frequency divider (Refer project files for the code)

- The PLL output clock is used as its own input clock, and the 100 MHz clock is divided into 1 MHz clocks.

- Repeat (7) to create div_us.bsf

- Create a new 1000 frequency division verilog file: div_1000f.v

- Create div_1000f.bsf symbol

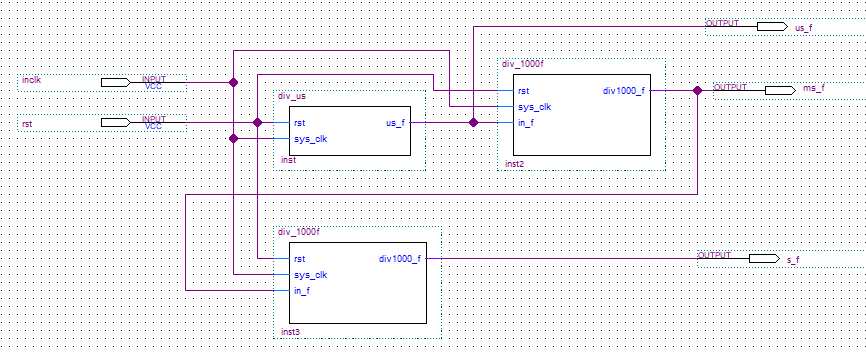

- Create the output pulse us, ms, second module, as shown in Figure 4.7. Refer the specific implementation to the reference code and the frequency division design of the experiment 1 and 3

- Create a new block/sch file block_div and add the designed graphic symbol file to block_div.bdf

- Repeat (7) to create the block_div.bsf symbol

Figure 4.7 us, ms, second pulse of block/sch design

- Create a new verilog file bcd_counter.v, design the hour and minute counter, and create the bsf symbol. Refer to previous experiments and implement part of the frequency division using block_div in (9).

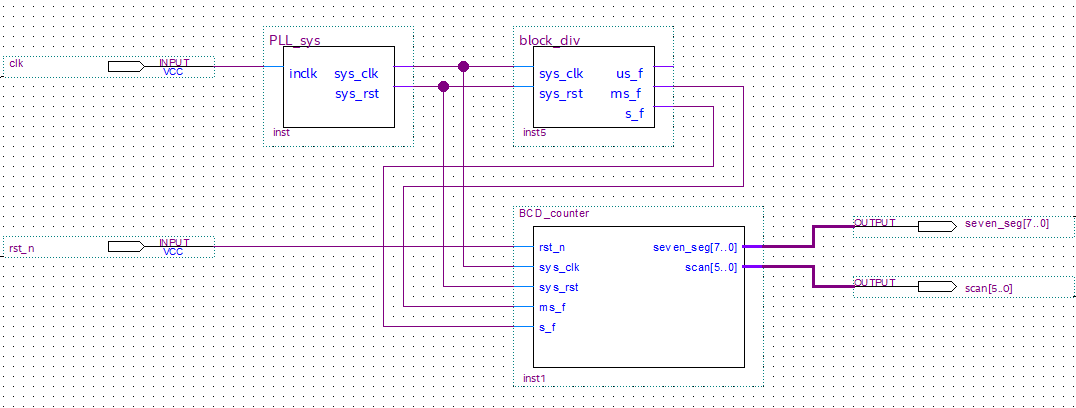

- Combine each *.bsf and complete the design of the digital clock (block_counter.bdf), as shown in Figure 4.8.

Figure 4.8 Digital clock for BDF design

4.4 Experiment Verification

Pin assignment, compilation, and program verification are consistent with Experiment 3. For reference, see Experiment 3, which is skipped here.