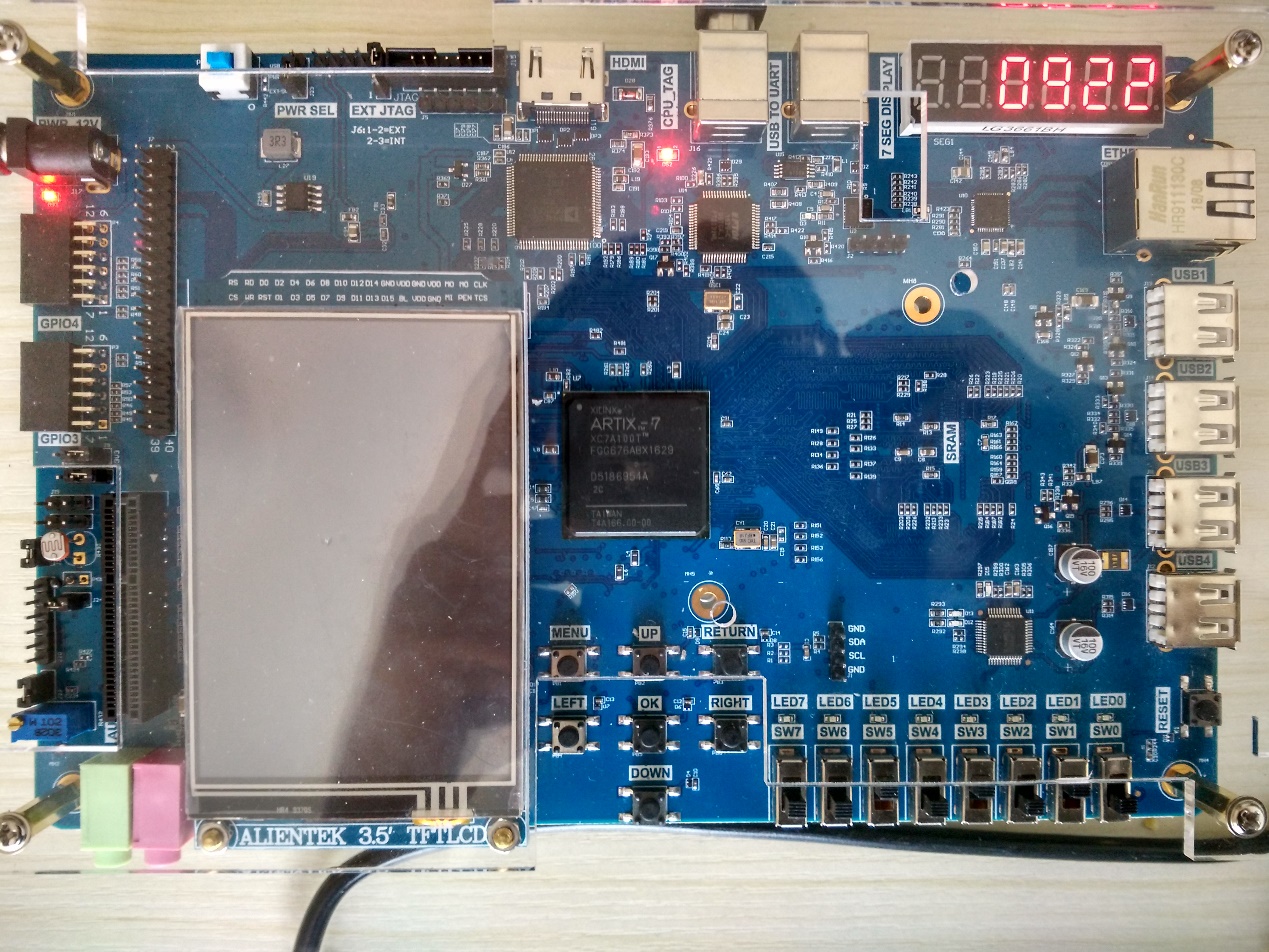

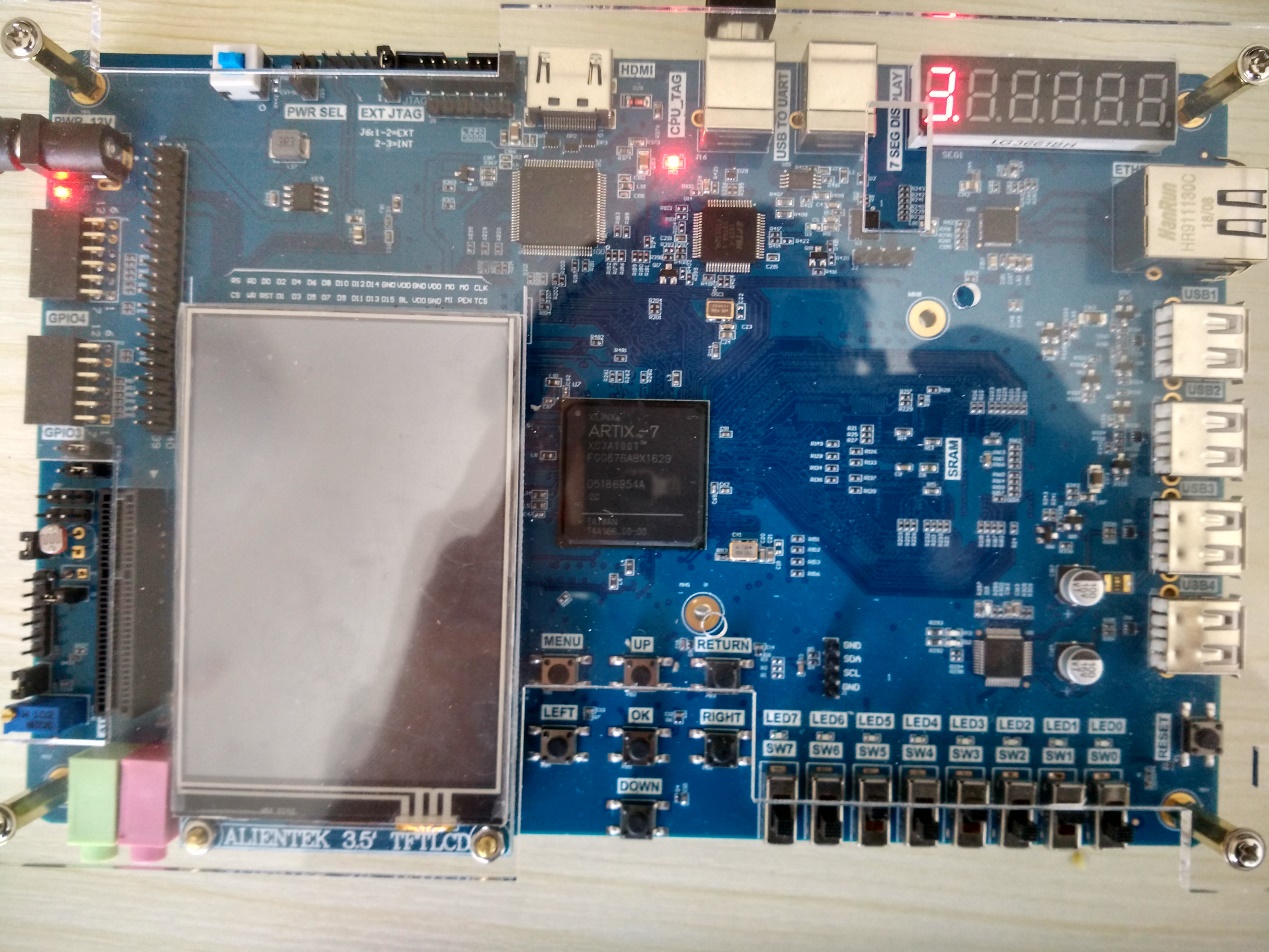

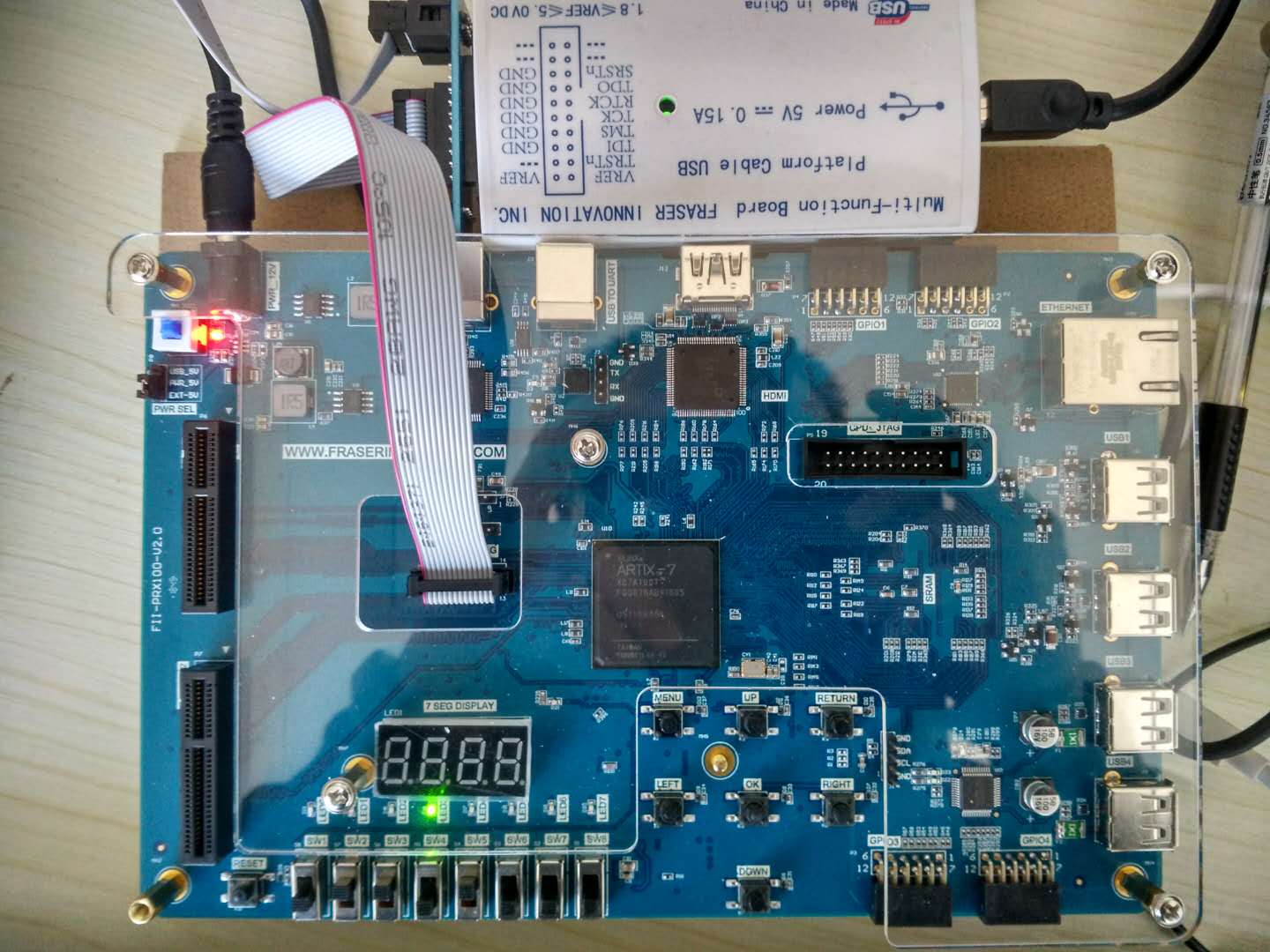

Xilinx Risc-V Board Tutorial : Button Debounce Design and Experimental- FII-PRX100 FPGA Board Experiment 5

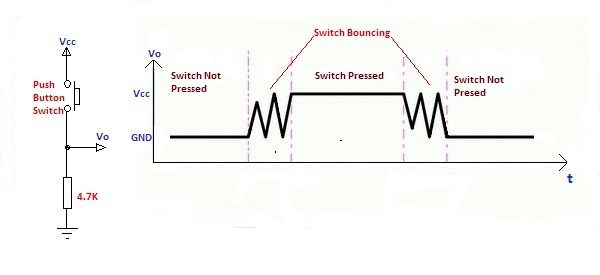

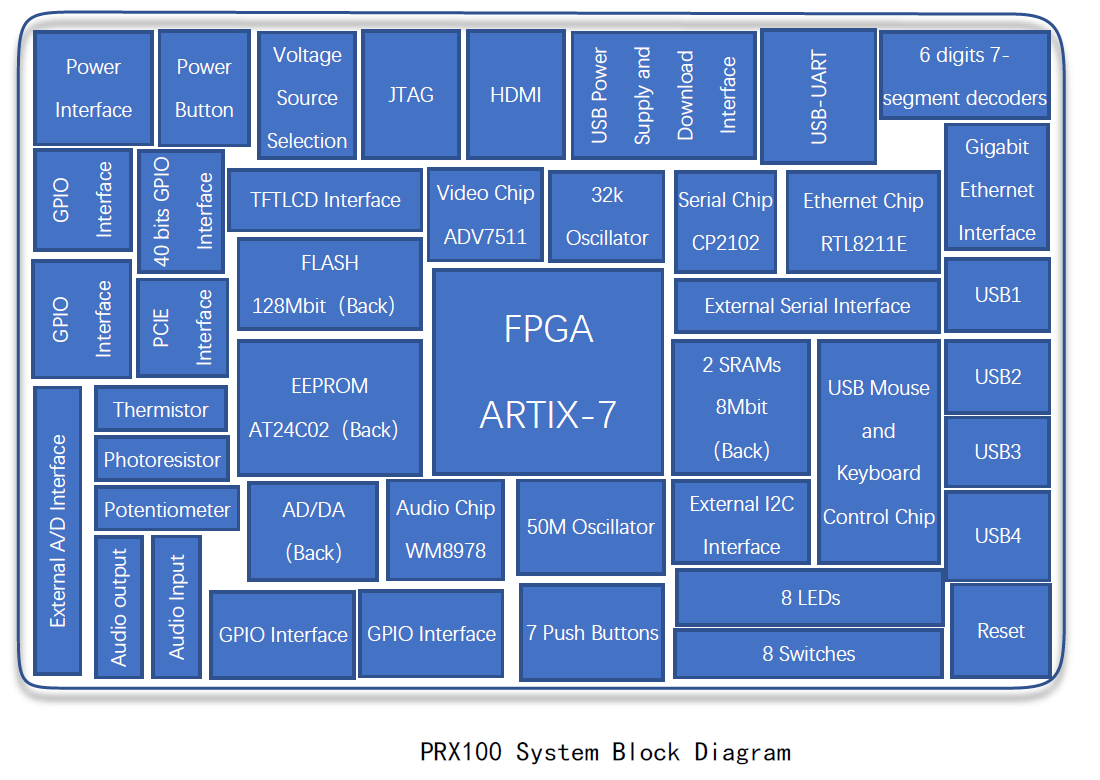

Experiment 5 Button Debounce Design and Experimental 1.Experiment Objective Review the design of blinking LED Learn the principle of button debounce, and adaptive programming Learn the connection and use of the FII-PRX100T button schematics Integrated application of button debounce and another compatible program design 2.Experiment Button debounce principle Usually, the switches used for the buttons are mechanical elastic switches. When the mechanical contacts are opened and closed, due to the elastic action of the mechanical contacts, a push button switch does not immediately turn on when closed, nor is it…

Read More