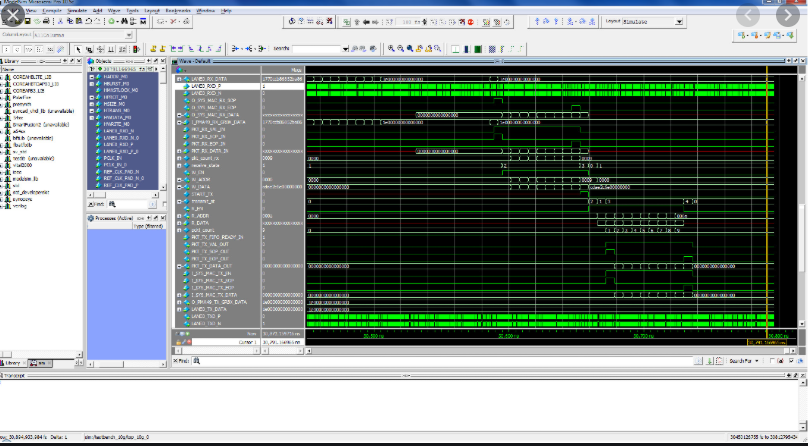

ModelSim

ModelSim is a multi-language HDL simulation environment by Mentor Graphics,for simulation of hardware description languages such as VHDL, Verilog and SystemC, and includes a built-in C debugger.

ModelSim can be used independently, or in conjunction with Intel Quartus Prime, Xilinx ISE or Xilinx Vivado. Simulation is performed using the graphical user interface (GUI), or automatically using scripts.

ModelSim uses a unified kernel for simulation of all supported languages, and the method of debugging embedded C code is the same as VHDL or Verilog.

In addition to supporting standard HDLs, ModelSim increases design quality and debug productivity. ModelSim’s award-winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design. Its architecture allows platform-independent compile with the outstanding performance of native compiled code.

ModelSim and Questa Sim products enable simulation, verification and debugging for the following languages:

- VHDL

- Verilog

- Verilog 2001

- SystemVerilog

- PSL

- SystemC

ModelSim Overview [1]

- Unified mixed language simulation engine for ease of use and performance

- Native support of Verilog, SystemVerilog for design, VHDL, and SystemC for effective verification of sophisticated design environments

- Fast time-to-debug, easy to use, multi-language debug environment

- Advanced code coverage and analysis tools for fast time to coverage closure

- Interactive and Post-Sim Debug available so same debug environment used for both

- Powerful Waveform compare for easy analysis of differences and bugs

- Unified Coverage Database with complete interactive and HTML reporting and processing for understanding and debugging coverage throughout your project

- Coupled with HDL Designer and HDL Author for complete design creation, project management and visualization capabilities

For more information, Please check:

[1] https://www.mentor.com/products/fv/modelsim/