Configure and Use Dual-port RAM, Use Dual_port RAM to Read and Write Frame Data – FPGA Beginner Study Board PRA006, PRA010 Experiment 9

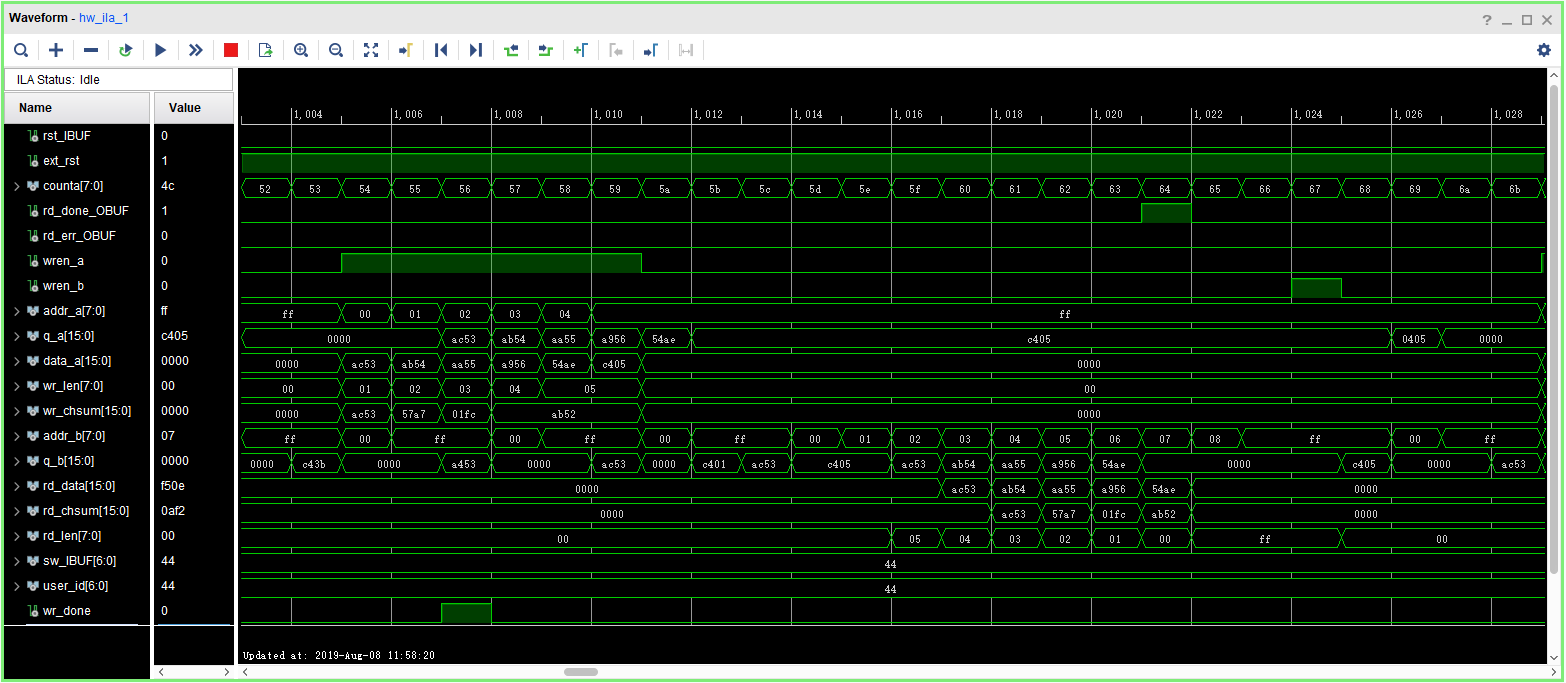

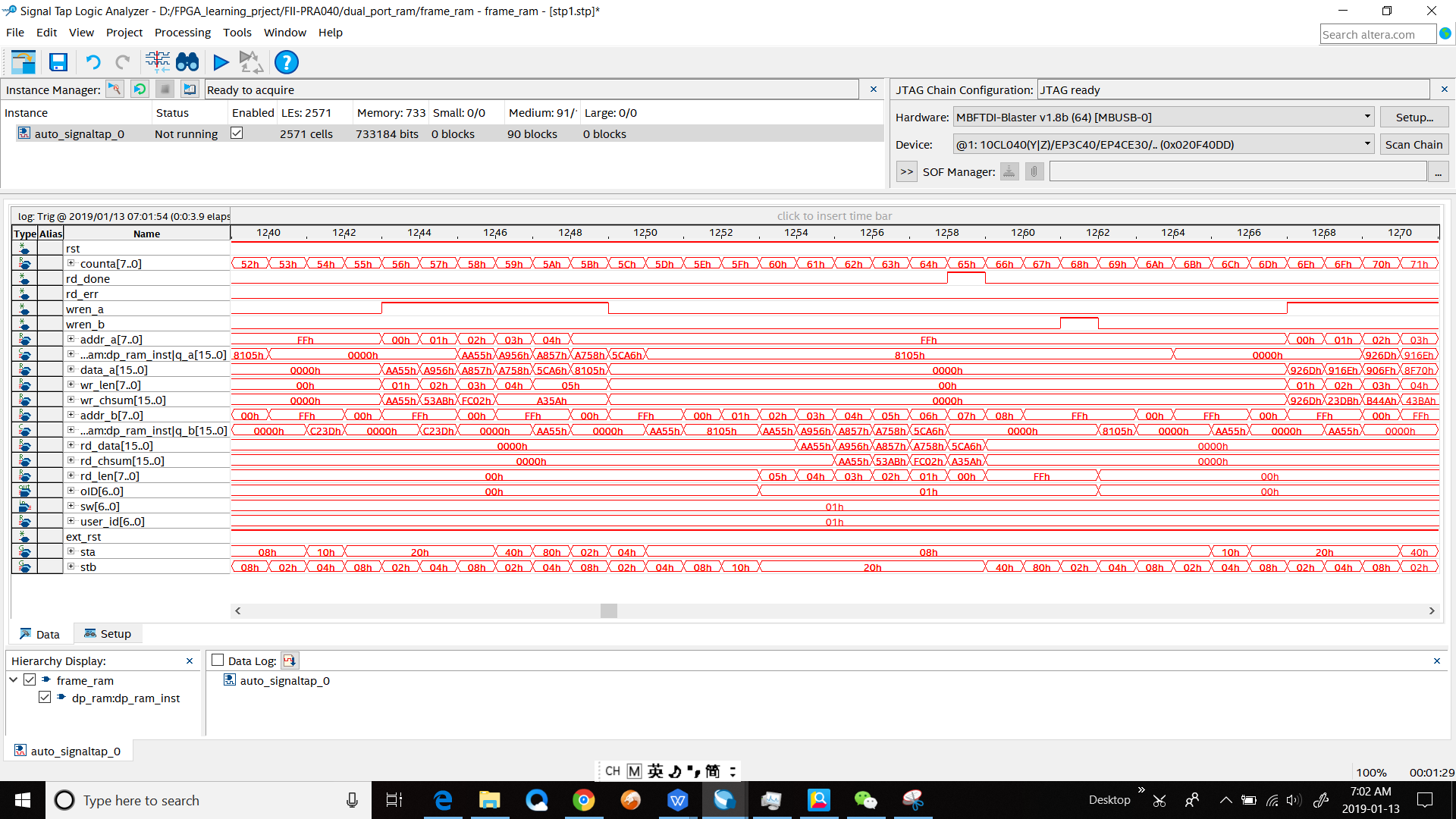

Experiment 9 Use Dual_port RAM to Read and Write Frame Data 9.1 Experiment Objective Learn to configure and use dual-port RAM Learn to use synchronous clock to control the synchronization of frame structure Learn to use asynchronous clock to control the synchronization of frame structure Experiment Implement Observing the synchronization structure of synchronous clock frames using SignalTap II Extended the use of dual-port RAM Design the use of three-stage state machine Design a 16-bit data frame Data is generated by an 8-bit counter: Data={~counta,counta} The ID of the data frame…

Read More