Understand What Ethernet is and How it Works, the Relationship Between Different Interface Types (MII, GMII, RGMII) , Ethernet Experiment – FPGA Beginner Study Board PRA006, PRA010 Experiment 14

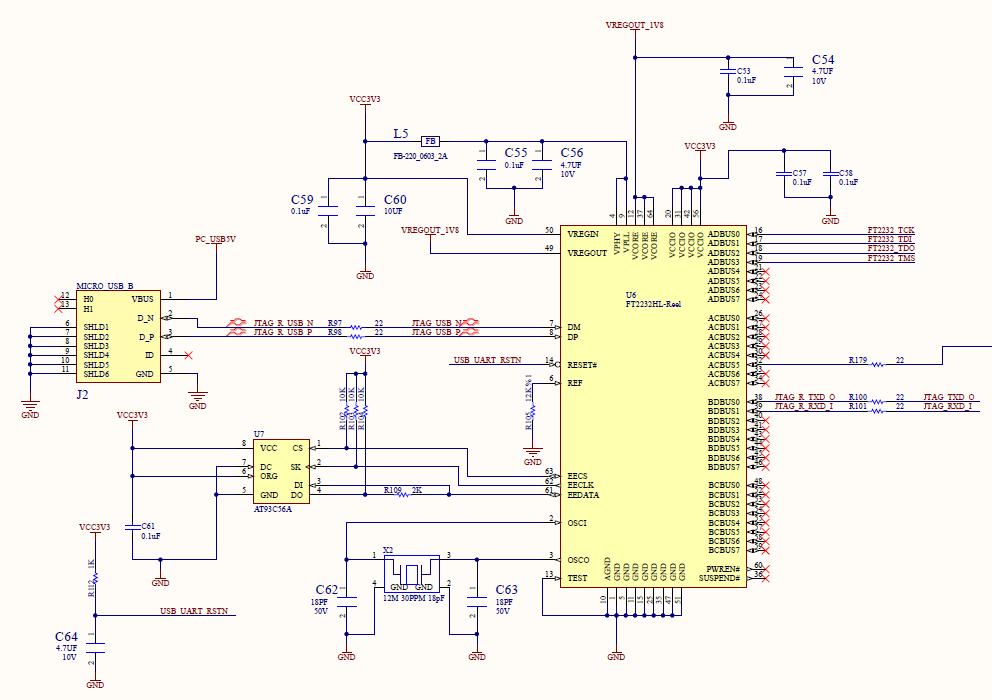

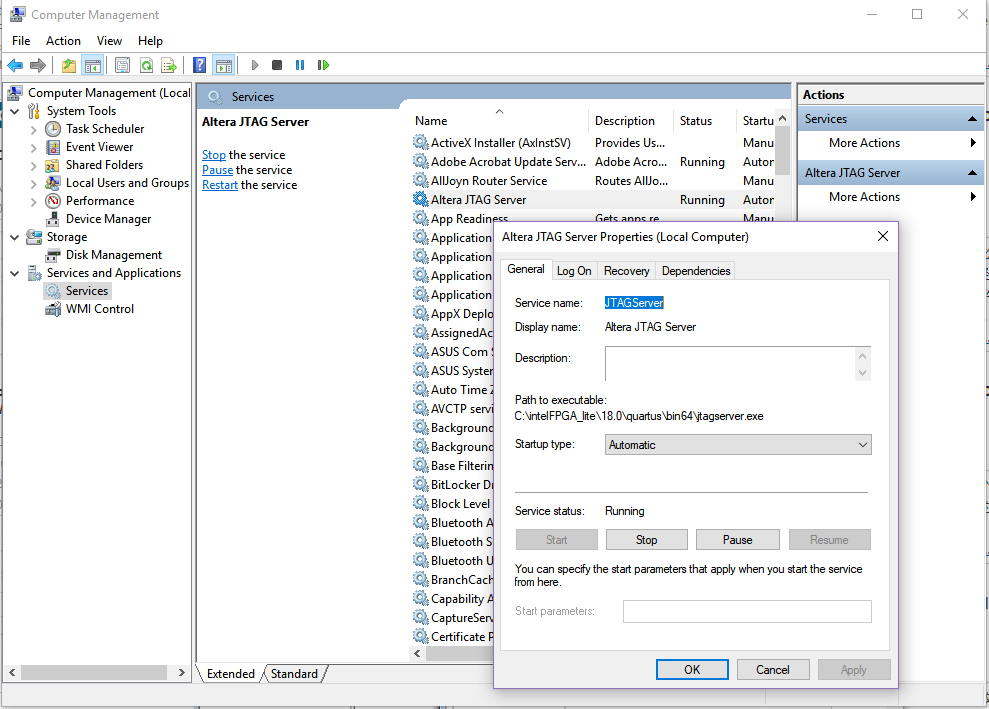

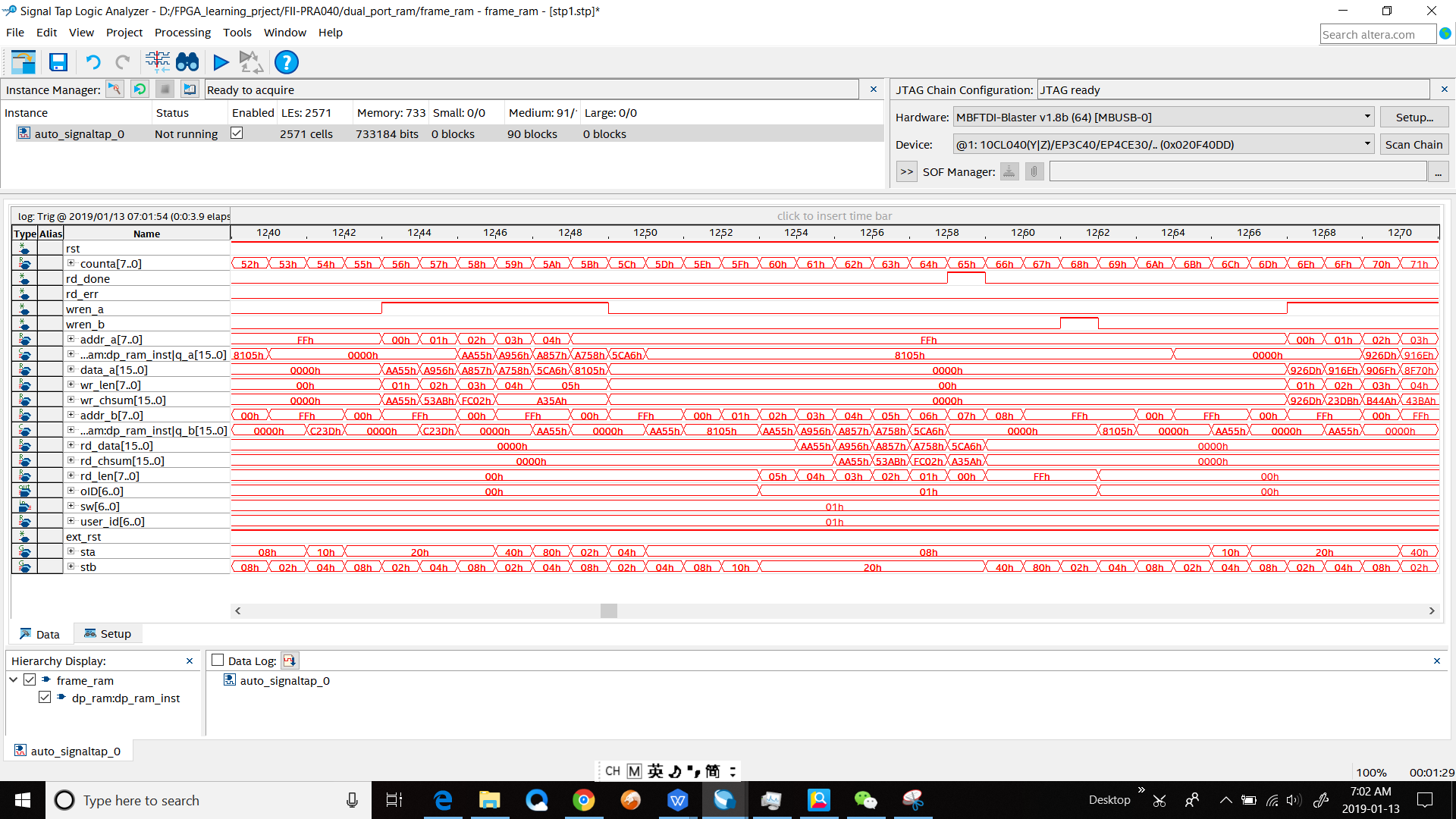

Experiment 14 Ethernet Experiment 14.1 Experiment Objective Understand what Ethernet is and how it works Familiar with the relationship between different interface types (MII, GMII, RGMII) and their advantages and disadvantages (the development board uses RGMII) Combine the development board to complete the transmission and reception of data and verify it 14.2 Experiment Implement Perform a loopback test to check if the hardware is working properly. Performing data verification Perform data transmission verification 14.3 Experiment 14.3.1 Experiment Principle Ethernet is a baseband LAN technology. Ethernet communication is a communication method…

Read More