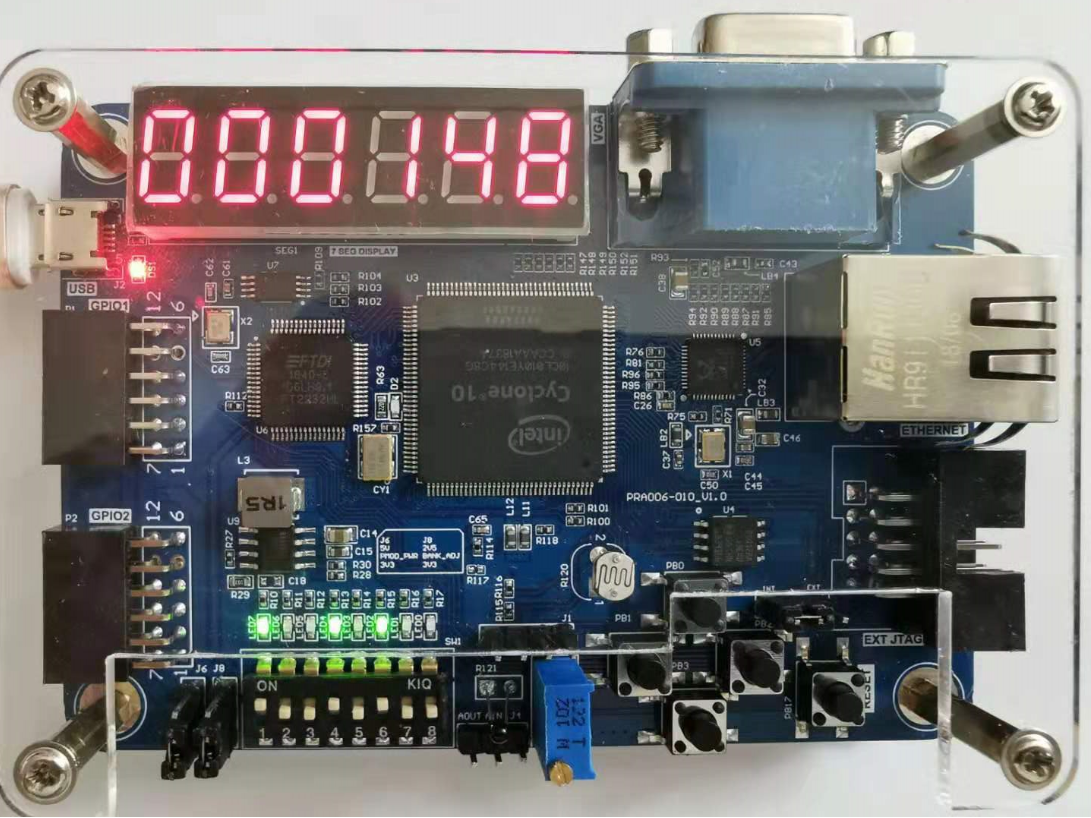

zynq xc7z030 board – FII-PE7030 Experiment 9 – Use Dual-port RAM to Read and Write Frame Data

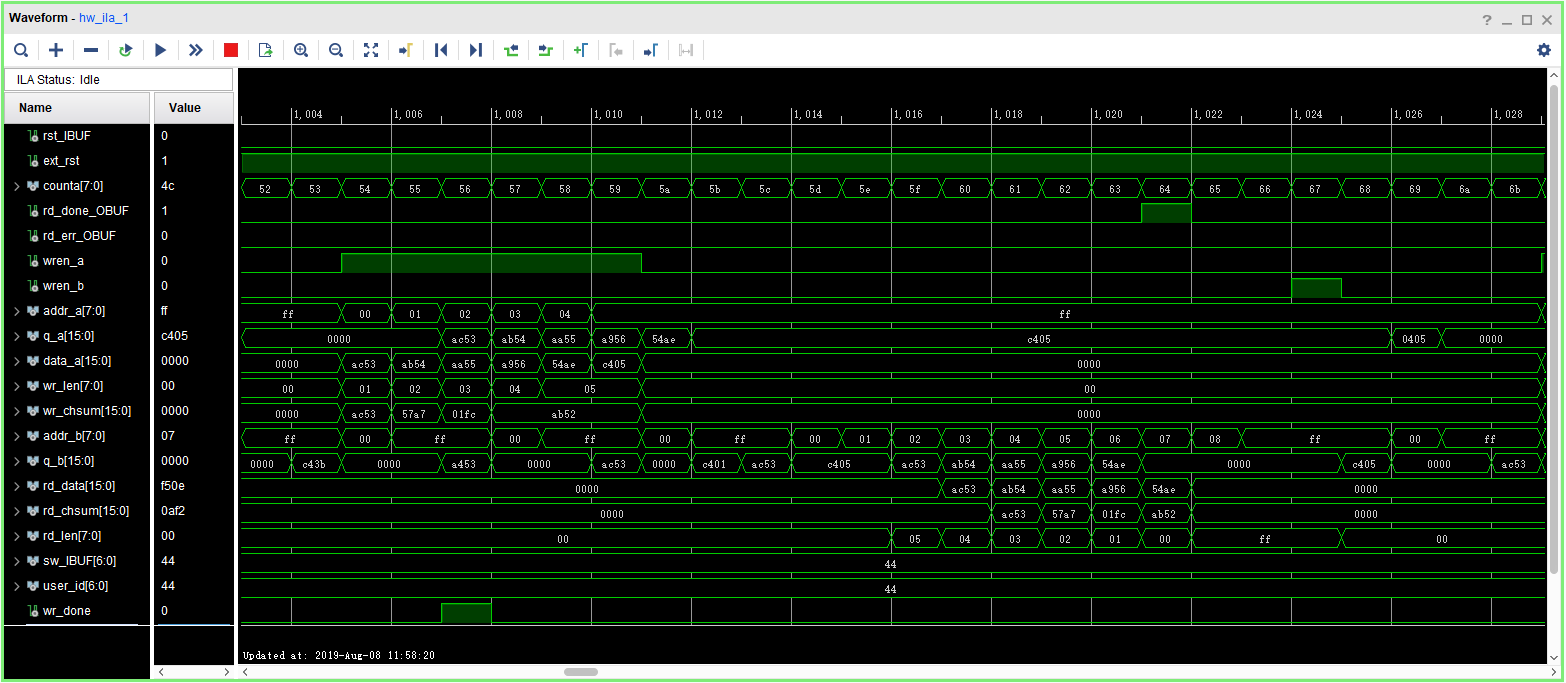

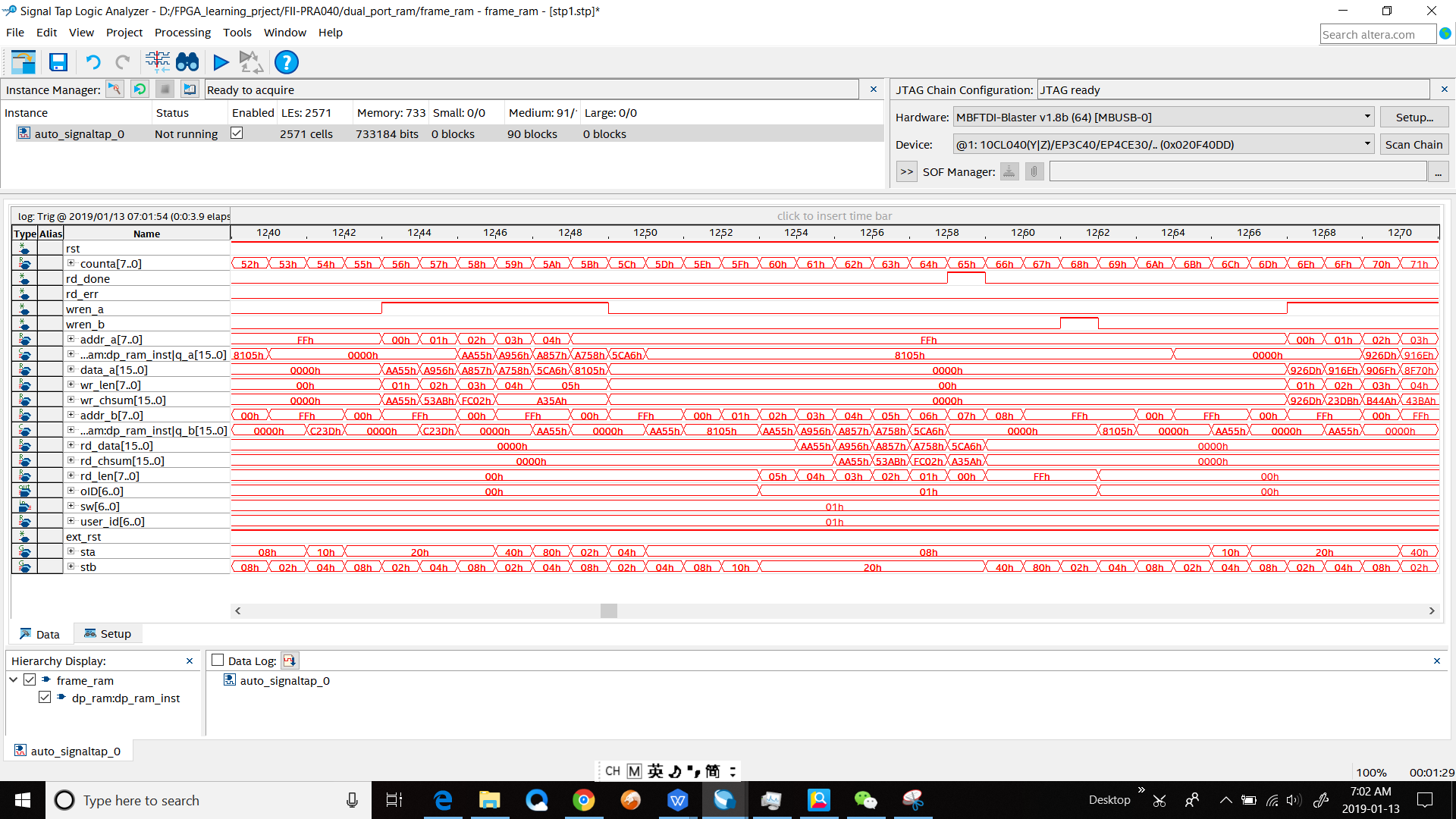

Experiment 9 Use Dual-port RAM to Read and Write Frame Data 9.1 Experiment Objective Learn to configure and use dual-port RAM Learn to use synchronous clock to control the synchronization of frame structure Learn to use asynchronous clock to control the synchronization of frame structure Use ILA to observe the structure of a synchronized clock frame Extended the use of dual-port RAM Design the use of three-stage state machine Experiment Implement Use ILA to observe the structure of a synchronized clock frame Extended the use of dual-port RAM Design the…

Read More