digital-to-analog conversion: DAC, analog-to-digital conversion: ADC – Xilinx Risc-V Board Tutorial : AD, DA Experiment – FII-PRX100 FPGA Board Experiment 13

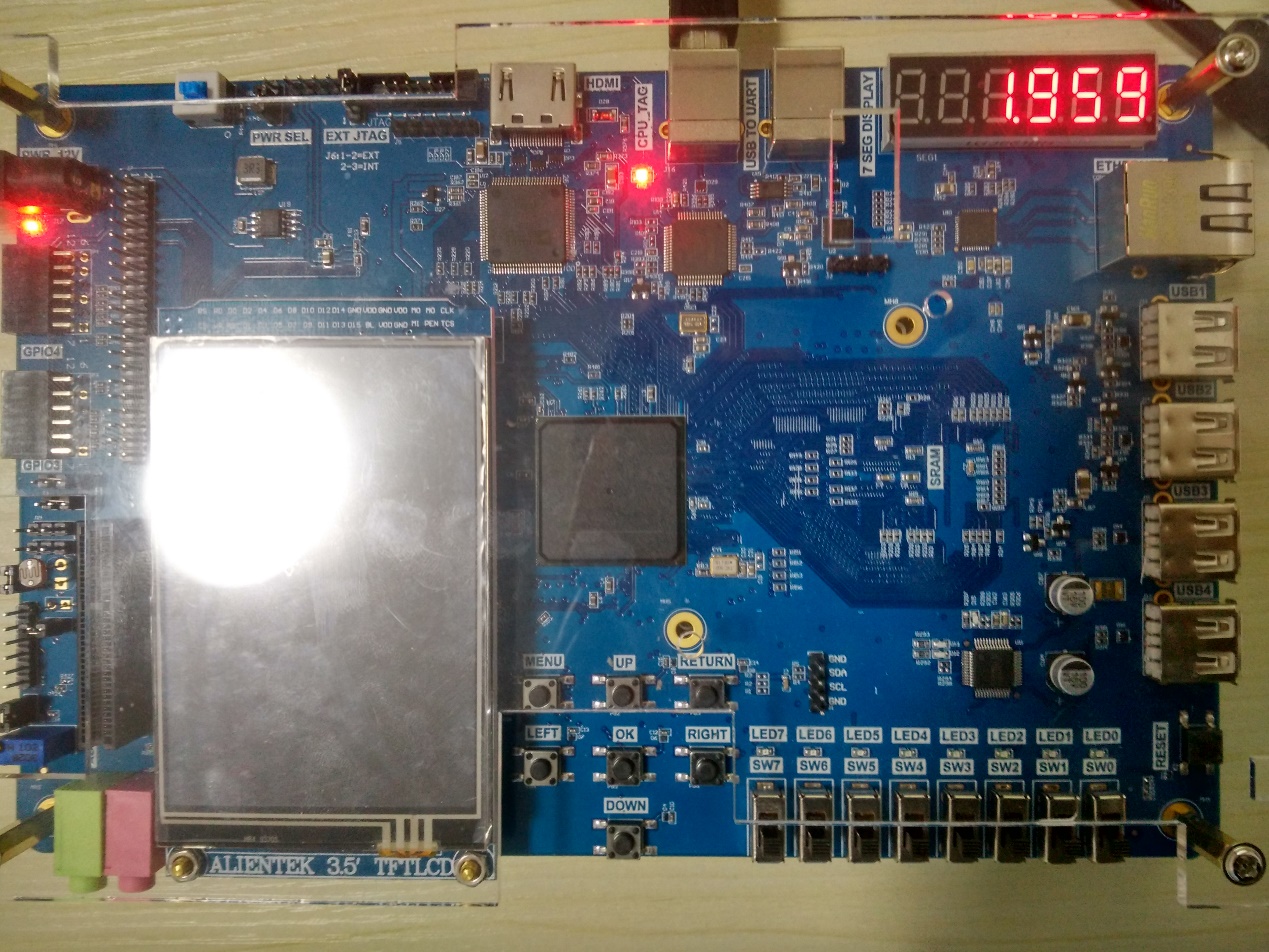

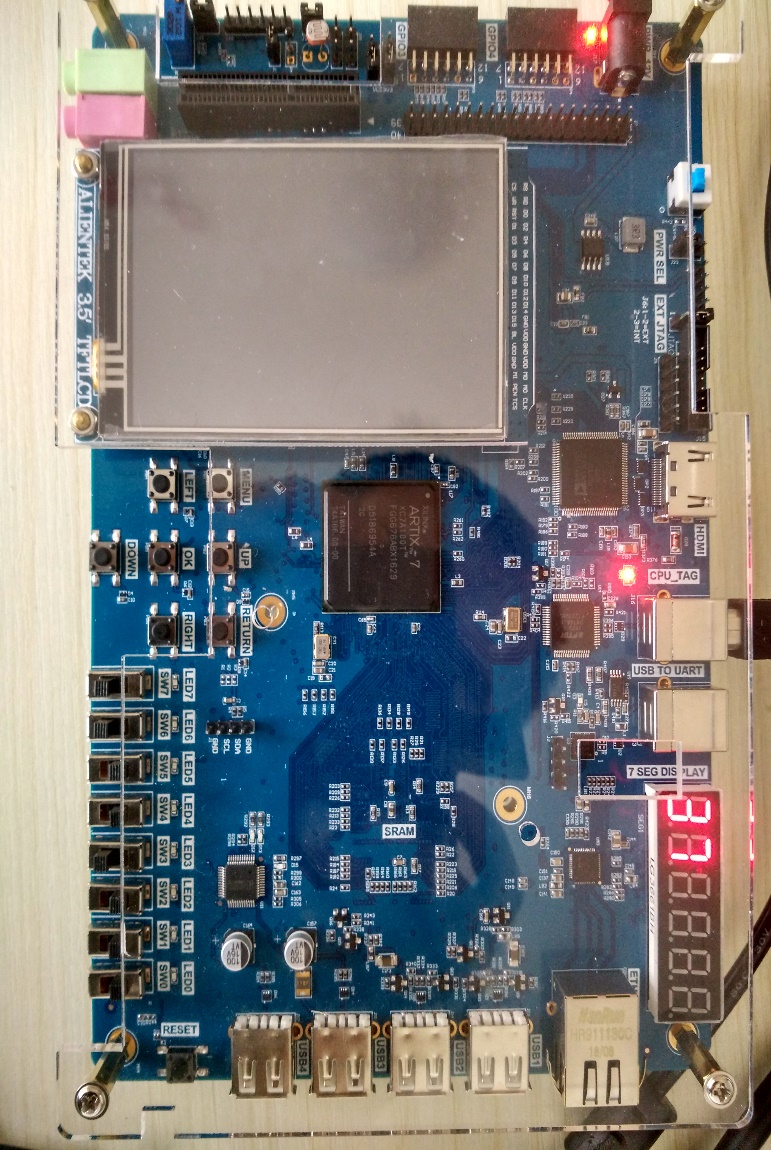

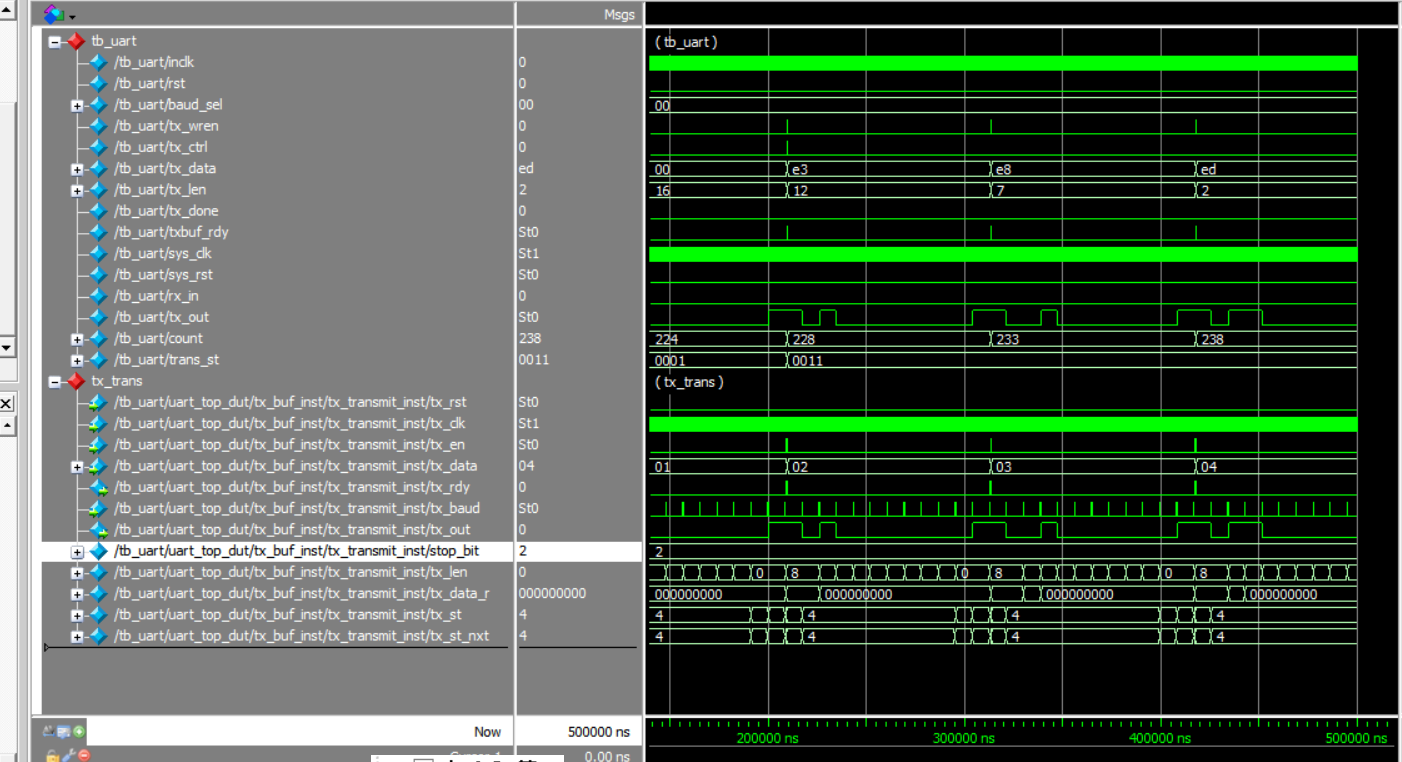

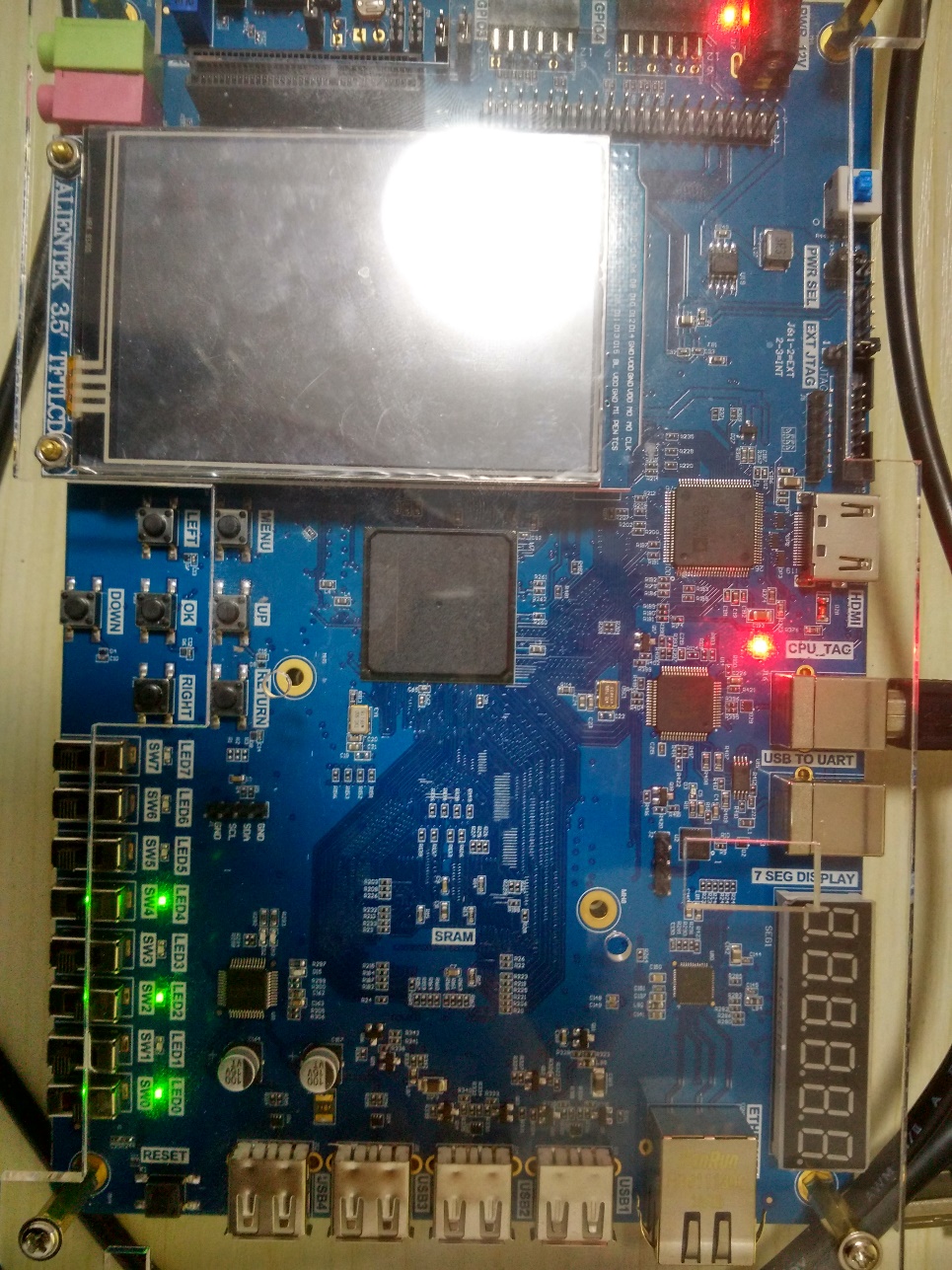

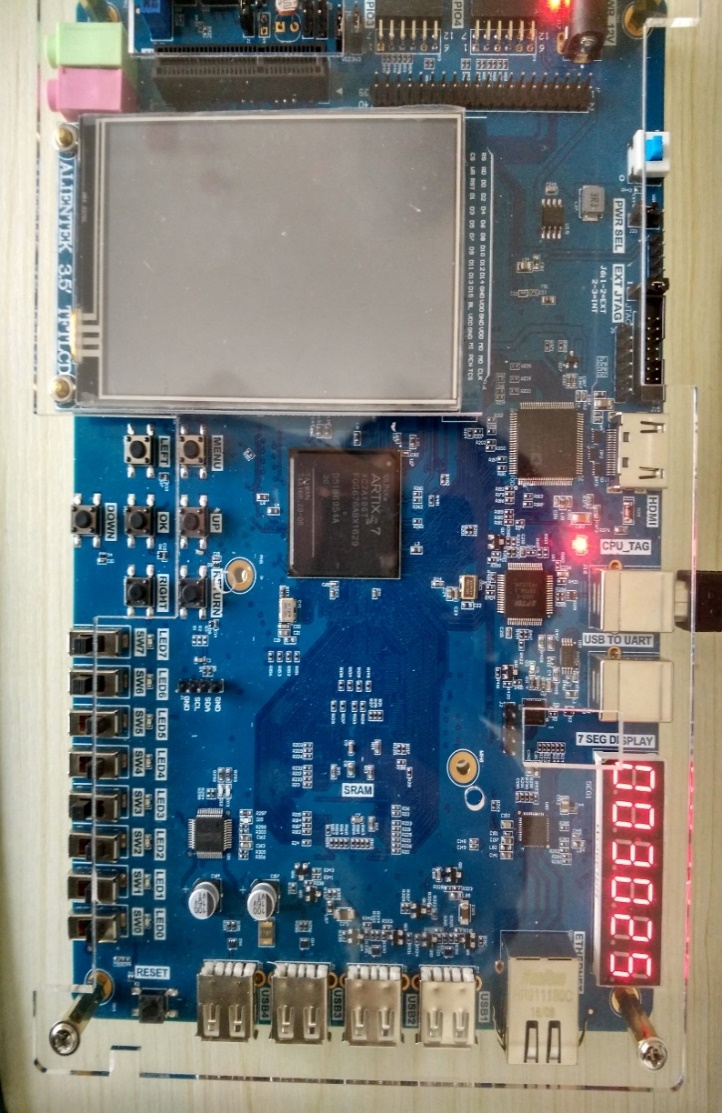

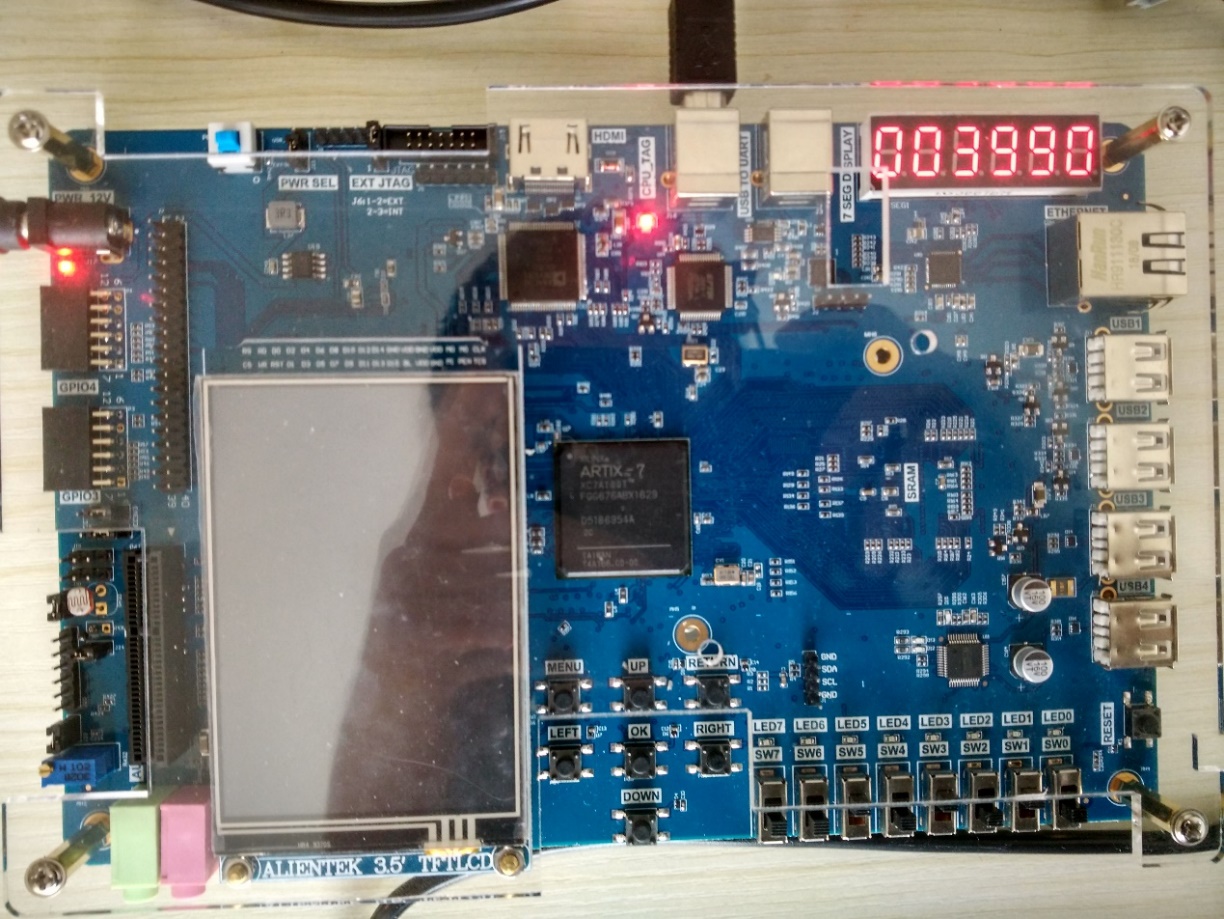

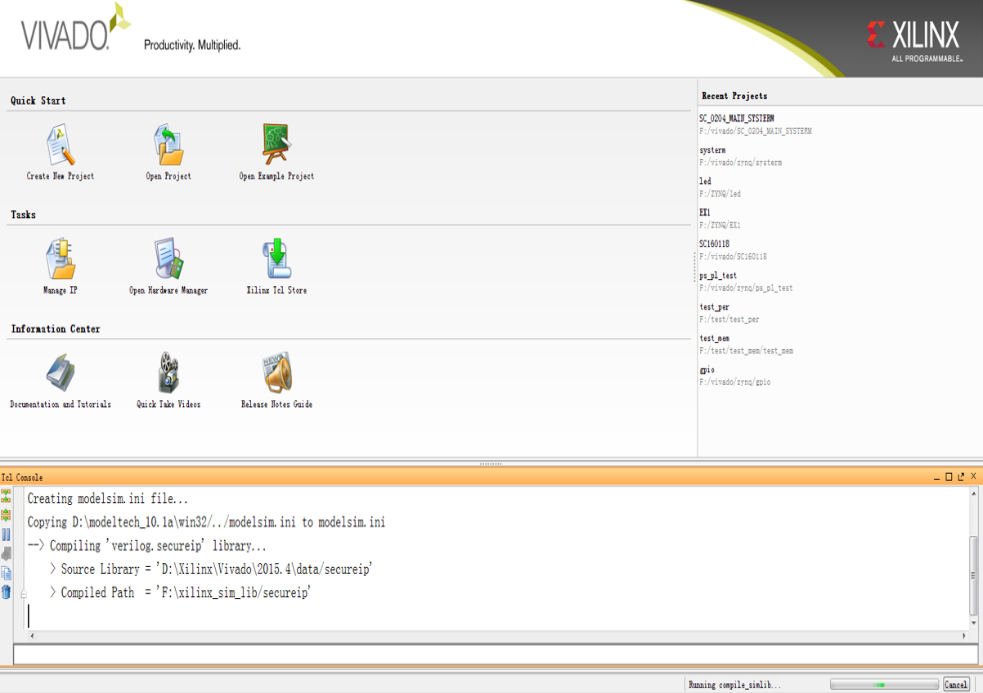

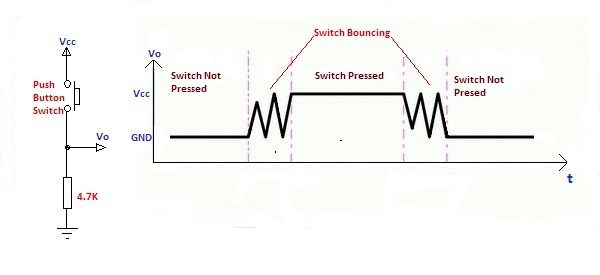

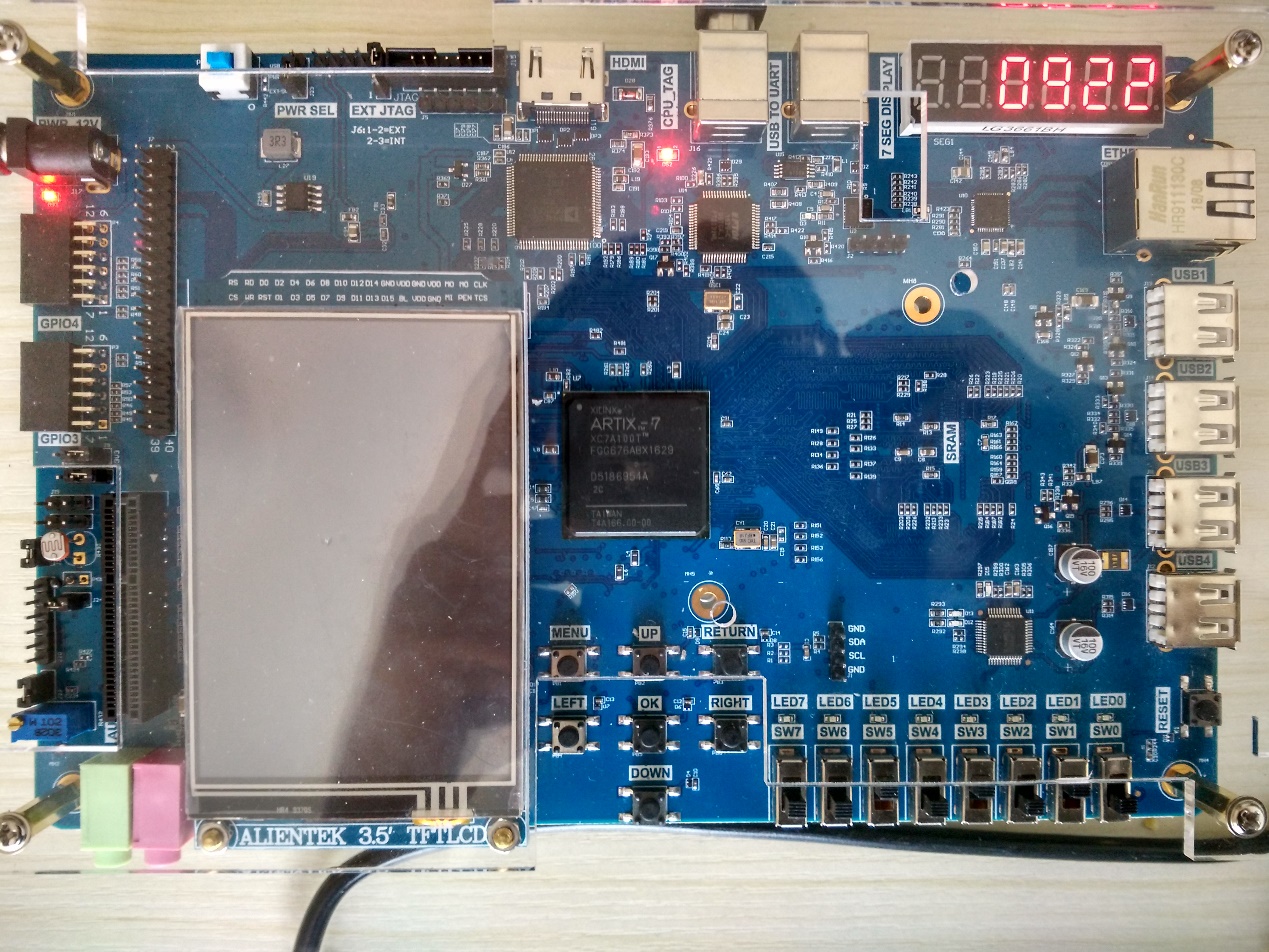

Experiment 13 AD, DA Experiment 1.Experiment Objective Since in the real world, all naturally occurring signals are analog signals, and all that are read and processed in actual engineering are digital signals. There is a process of mutual conversion between natural and industrial signals (digital-to-analog conversion: DAC, analog-to-digital conversion: ADC). The purpose of this experiment is twofold: Learning the theory of AD conversion Read the value of AD acquisition from PCF8591, and convert the value obtained into actual value, display it with segment decoders 2.Experiment Requirement Perform analog-to-digital conversion using…

Read More