RISC-V C Programming 1 (1)Introduction to FII-RISC-V CPU and C Project Compilation Process

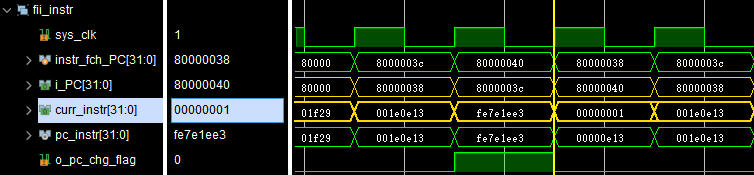

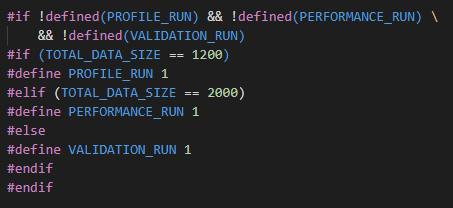

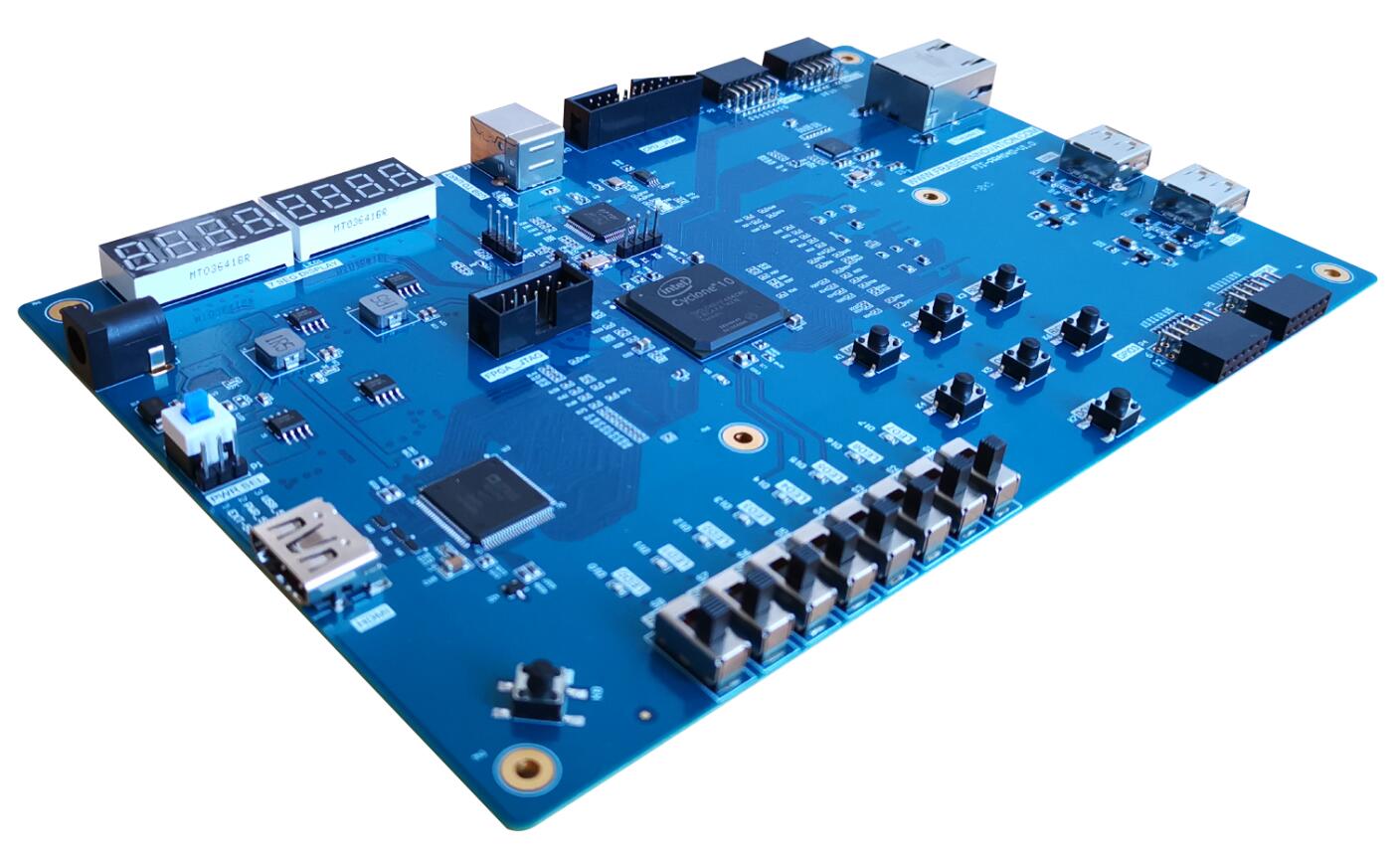

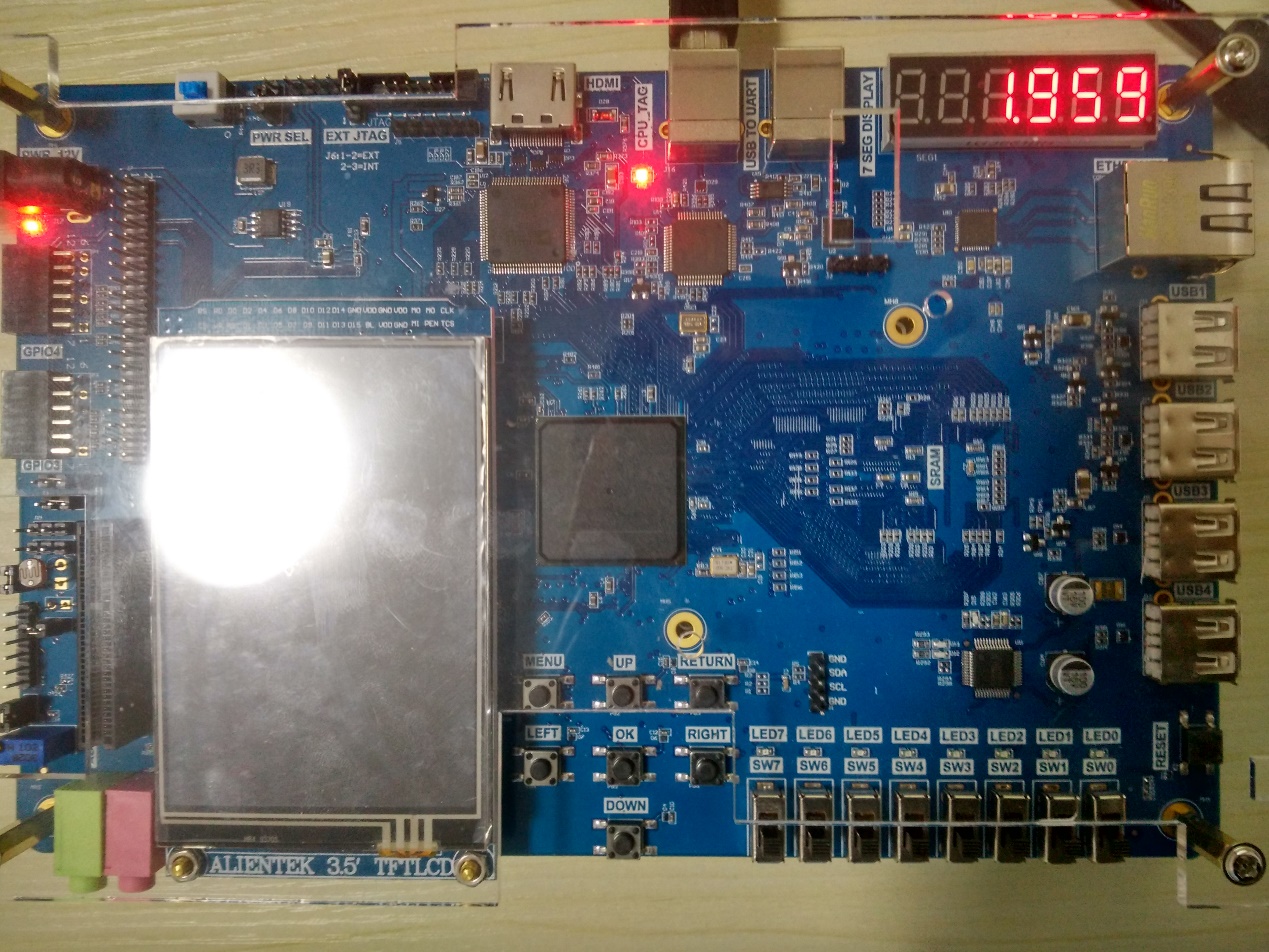

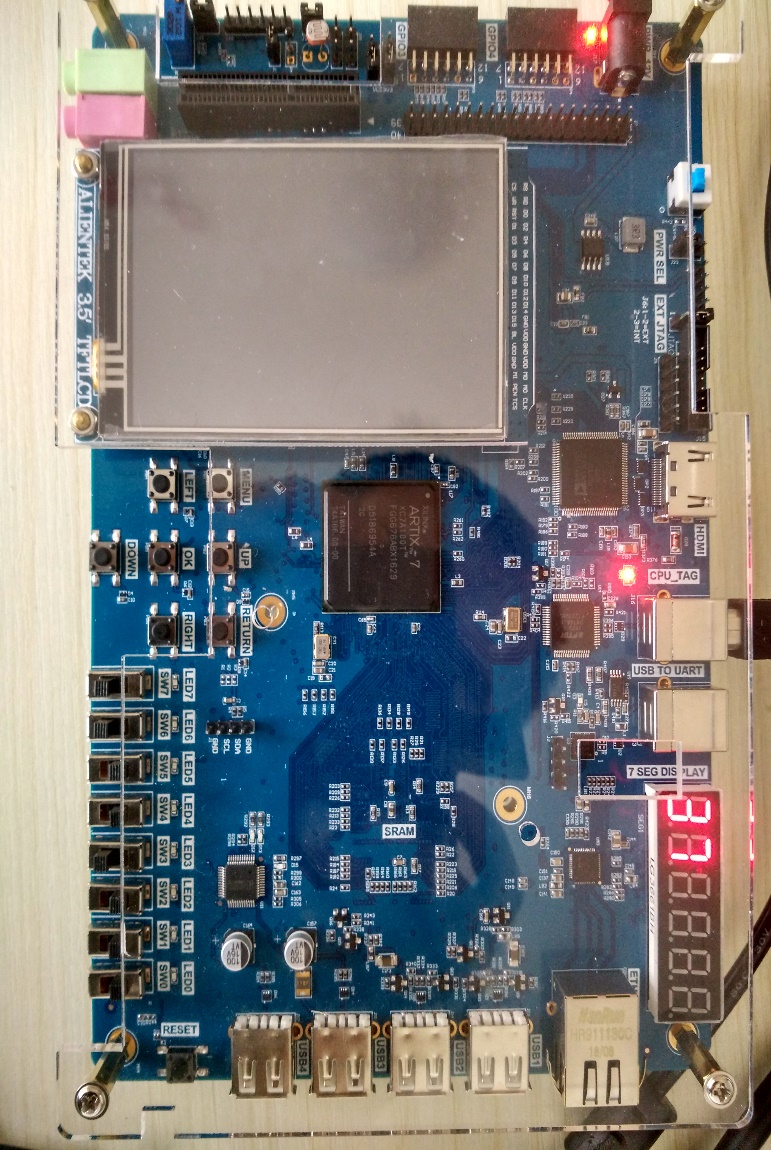

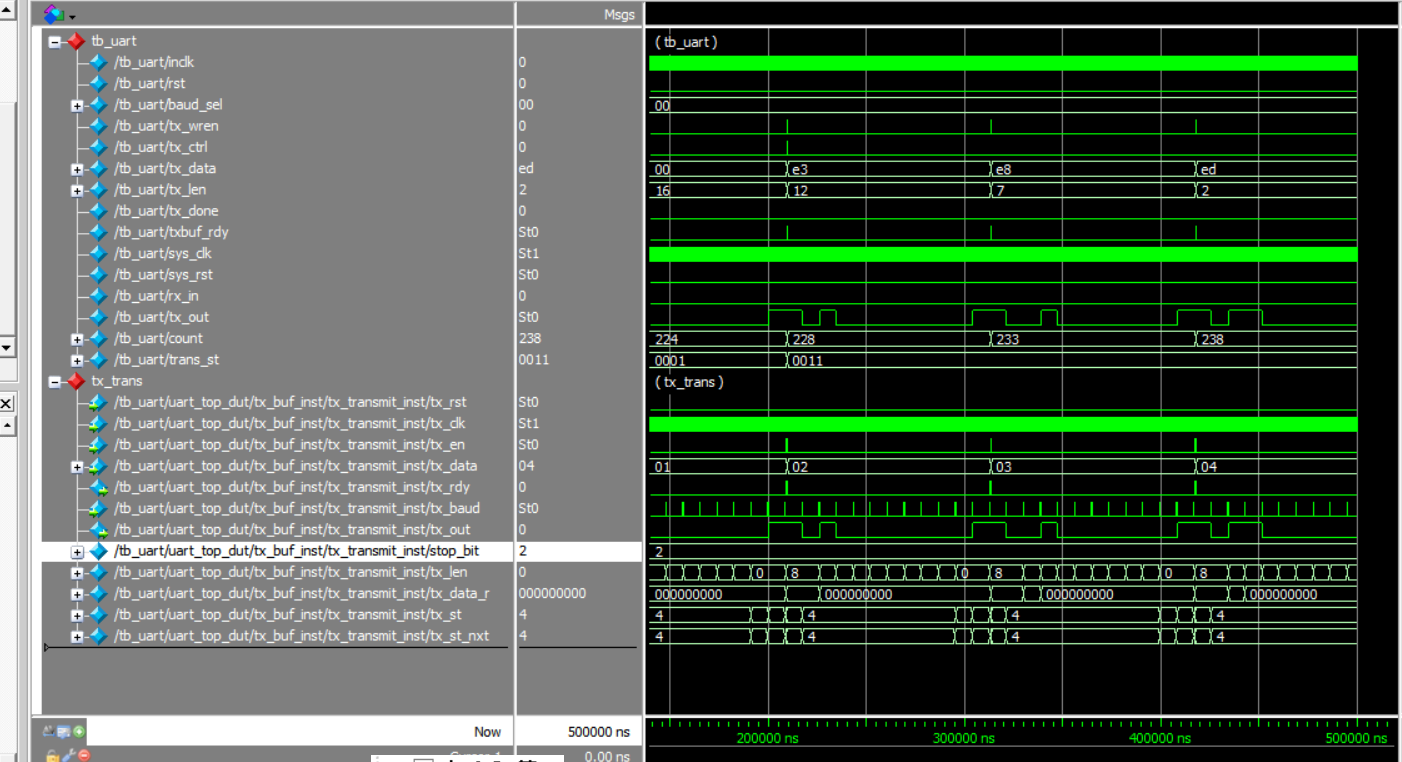

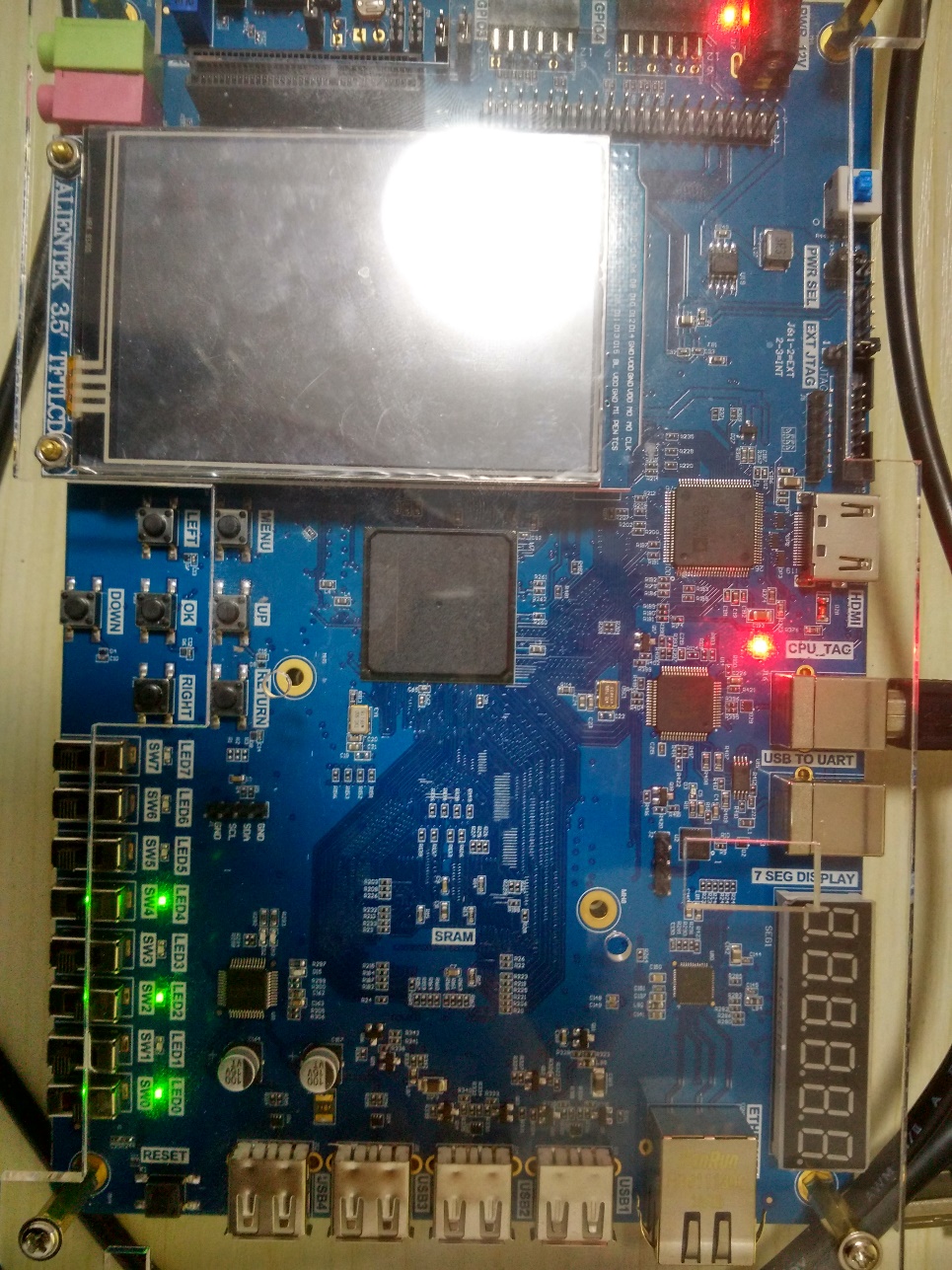

1.Introduction to FII-RISCV CPU Direct to Table of Contents: RISC-V Syllabus First of all, there is an overview of the CPU, FII-RISCV. RISCV is an open standard instruction set architecture (ISA) based on reduced instruction set computer (RISC) principles [1]. FII-RISCV is researched and developed following the RISCV standard. Here are some basic features about FII-RISCV: RV32I (32 registers that supports integer operations) Does not support multiplication instructions (the newest version do support) Does not support Atomic operations Does not support compressed instruction Supports software interrupt Supports…

Read More