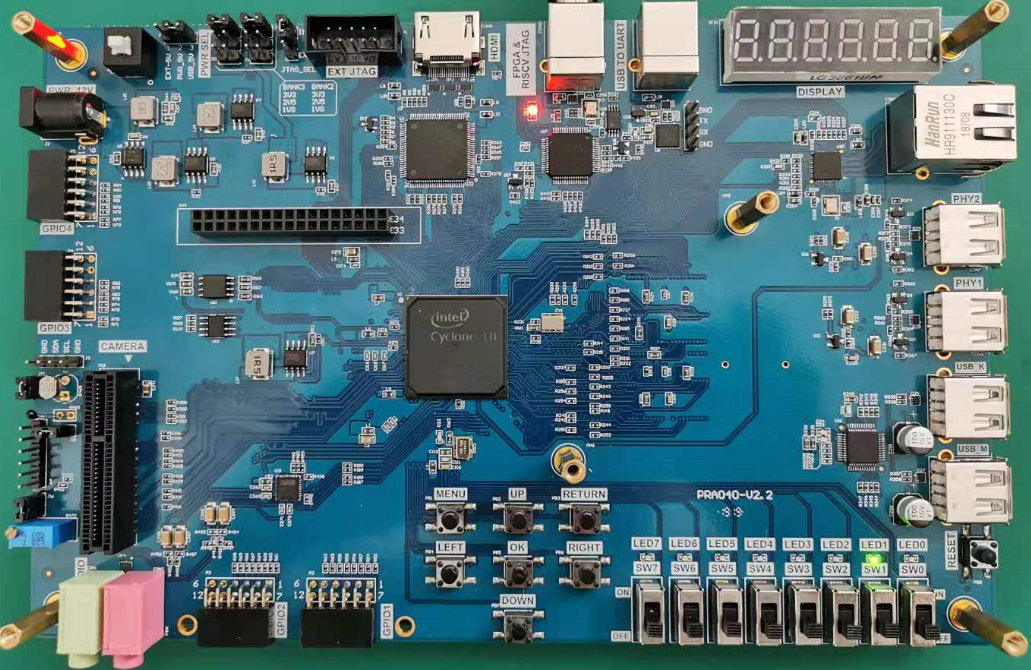

OV5640 Camera Photo Display Experiment, IIC bus, HDMI, Understand the power-on sequence of the OV5640 – FII-PRA040 Altera Risc-V Experiment 17

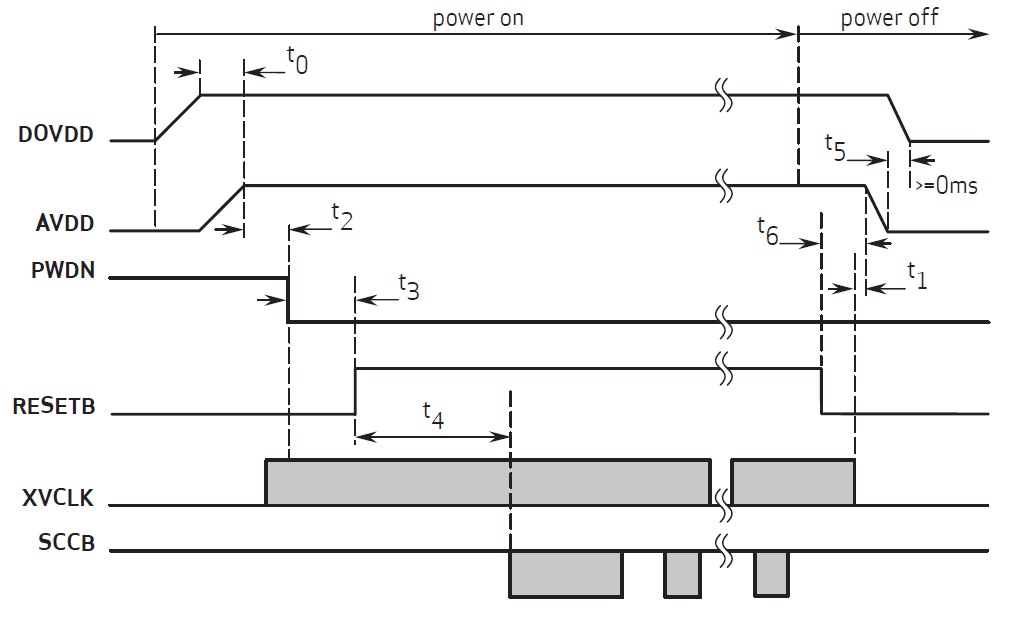

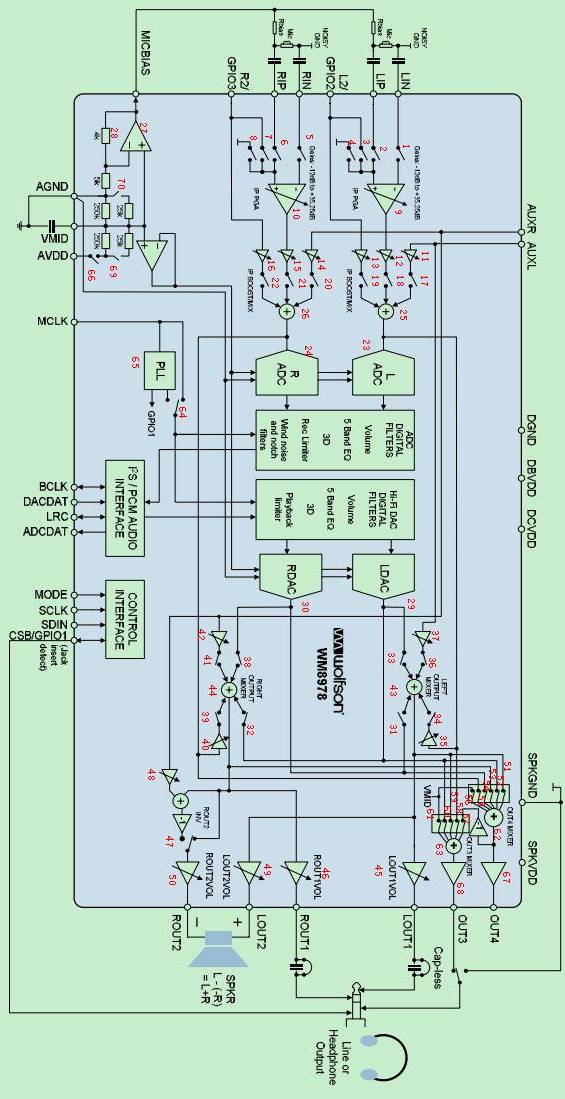

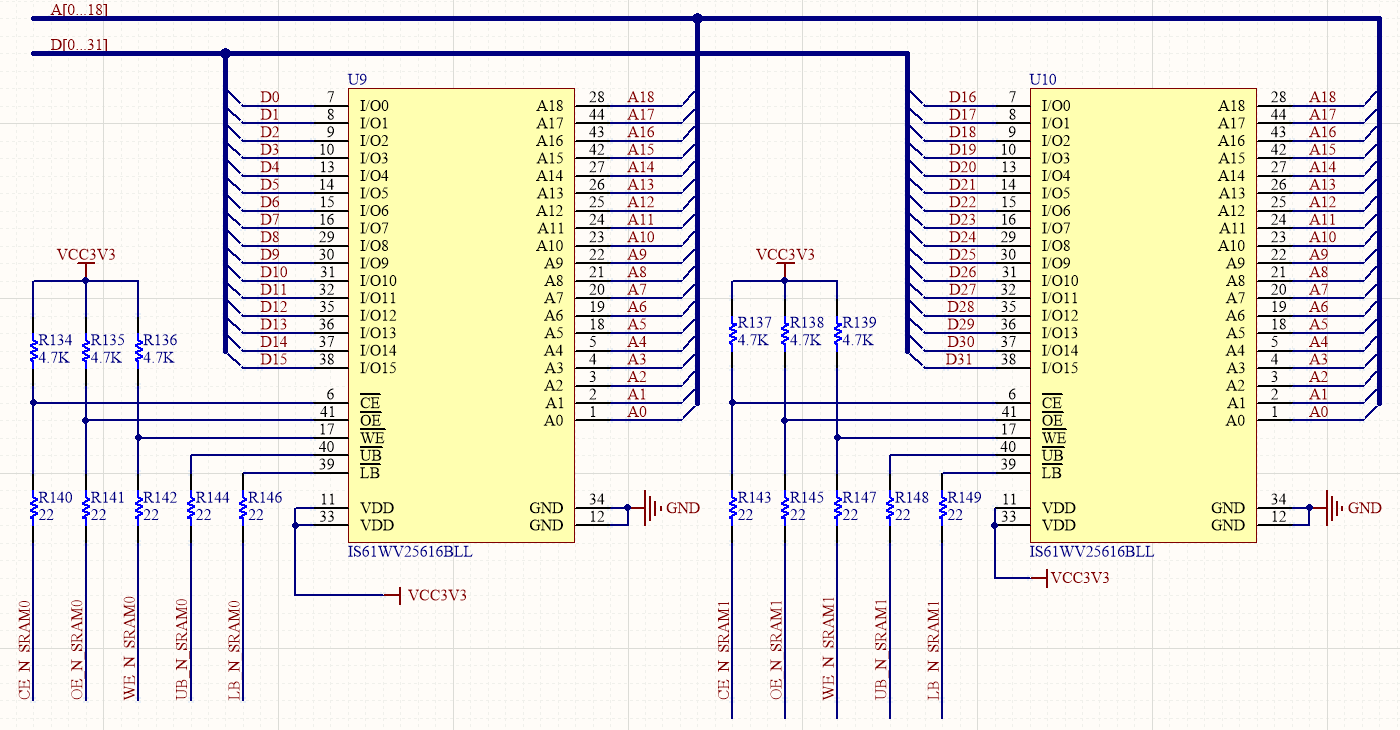

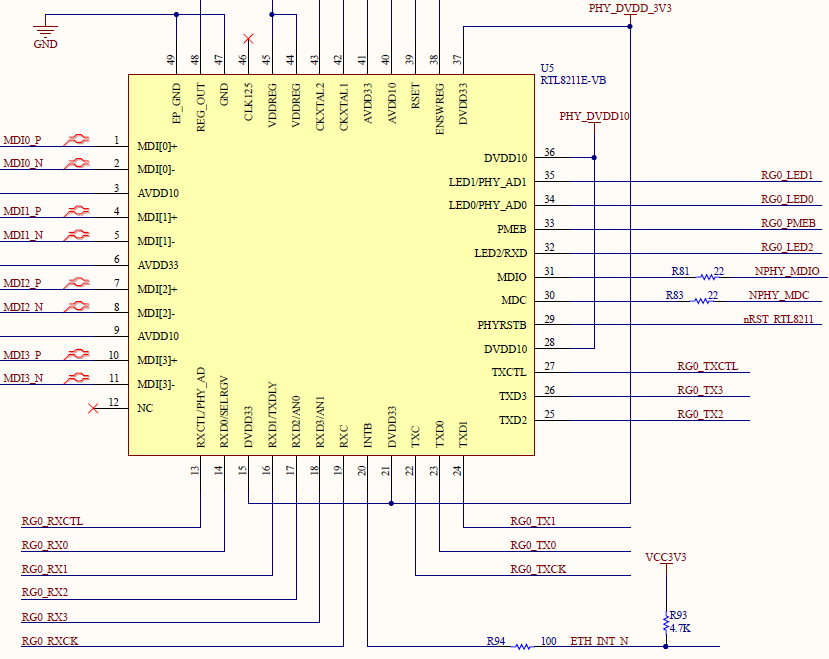

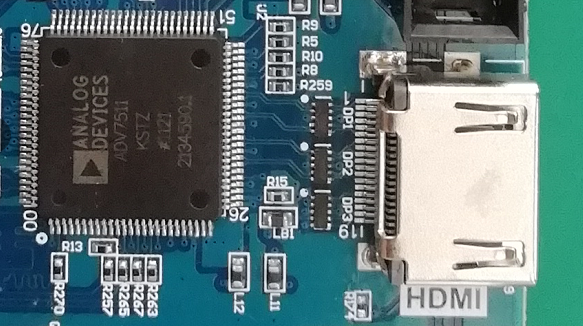

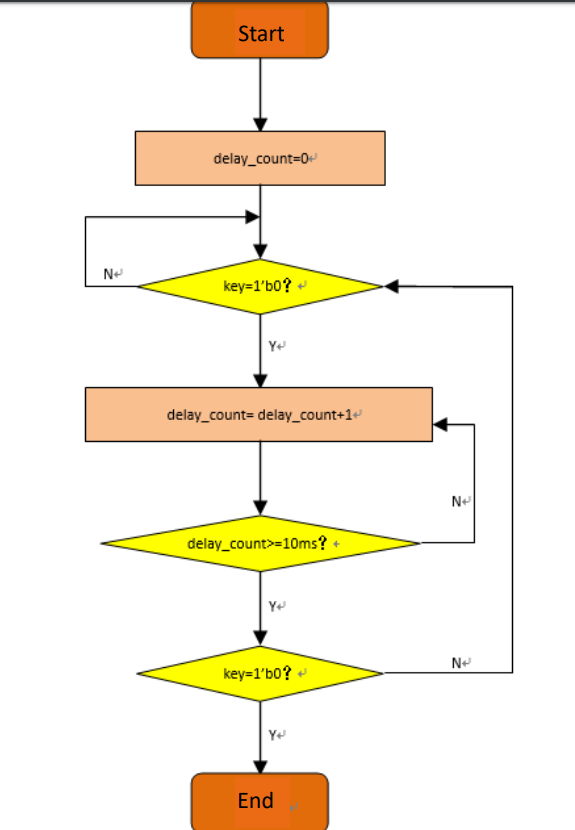

Experiment 17 Photo Display Experiment of OV5640 Camera 17.1 Experiment Objective Understand the power-on sequence of the OV5640 camera and the corresponding register configuration process when outputting images of different resolutions Review previous knowledge of IIC bus Review previous knowledge of HDMI 17.2 Experiment Implement Read the power-on sequence of the OV5640 datasheet, and correctly write the power-on control program according to the peripheral module schematics. Correctly write the configuration program of the OV5640 camera with a resolution of 640X480 according to the timing requirements of the SCCB interface Based…

Read More