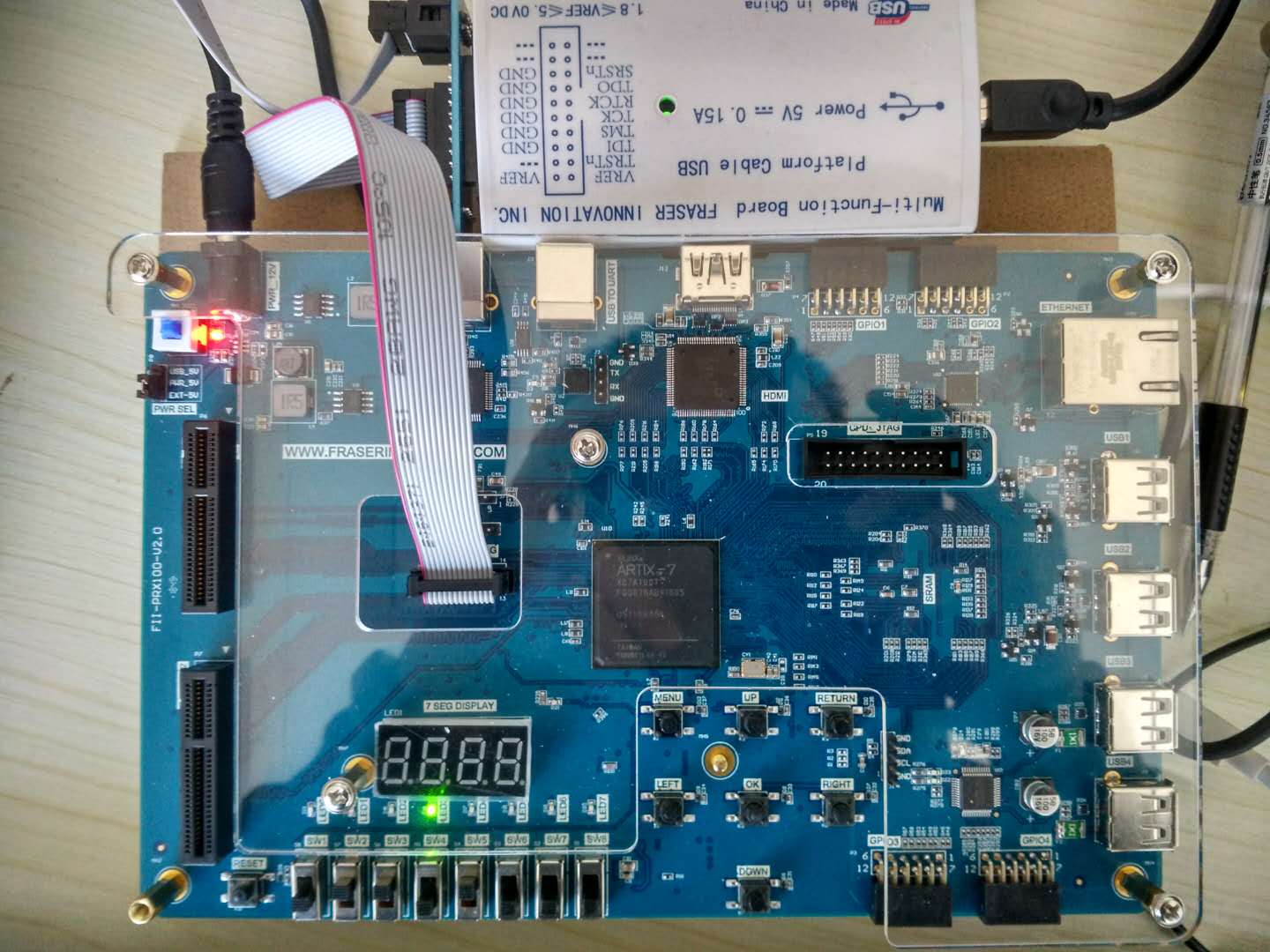

Xilinx Risc-V Board Tutorial : Asynchronous Serial Port Design and Experiment – FII-PRX100 FPGA Board Experiment 11

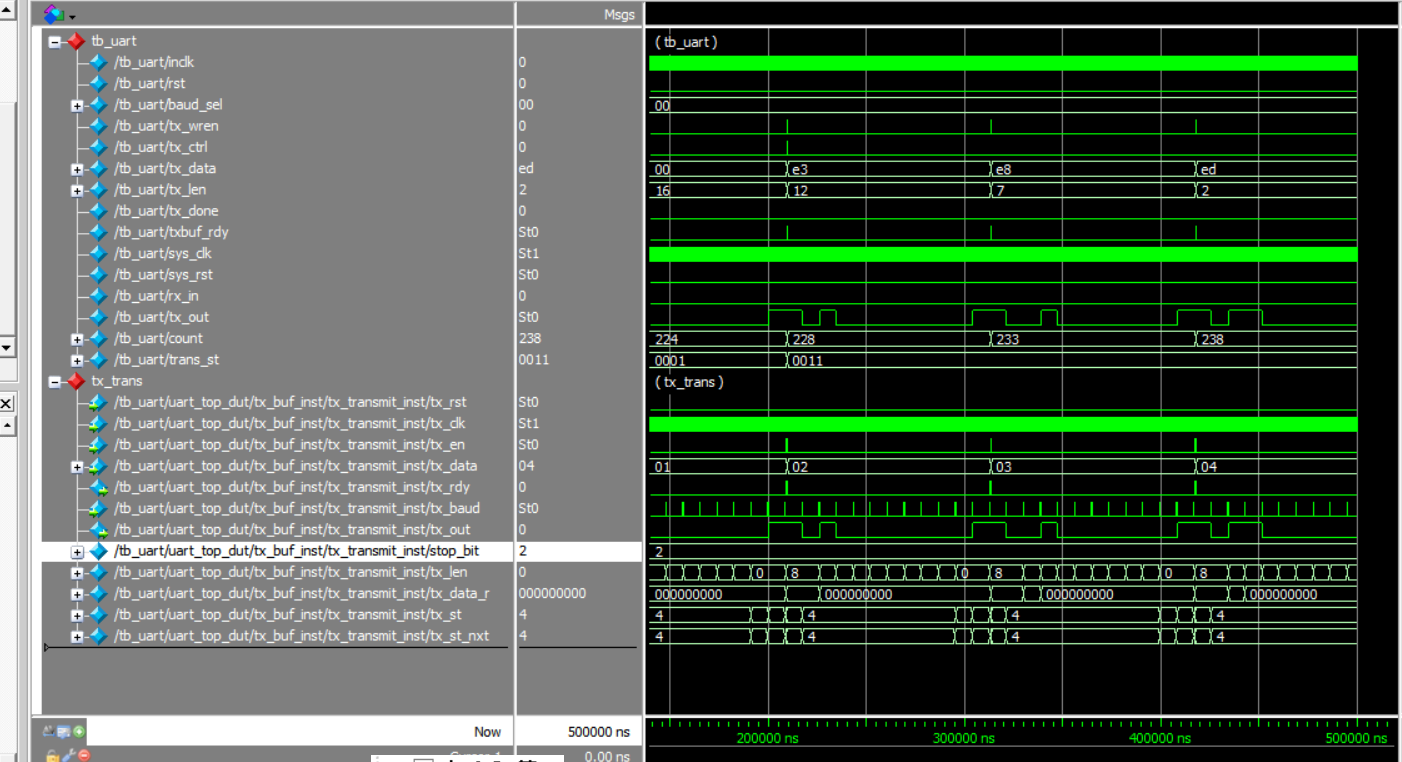

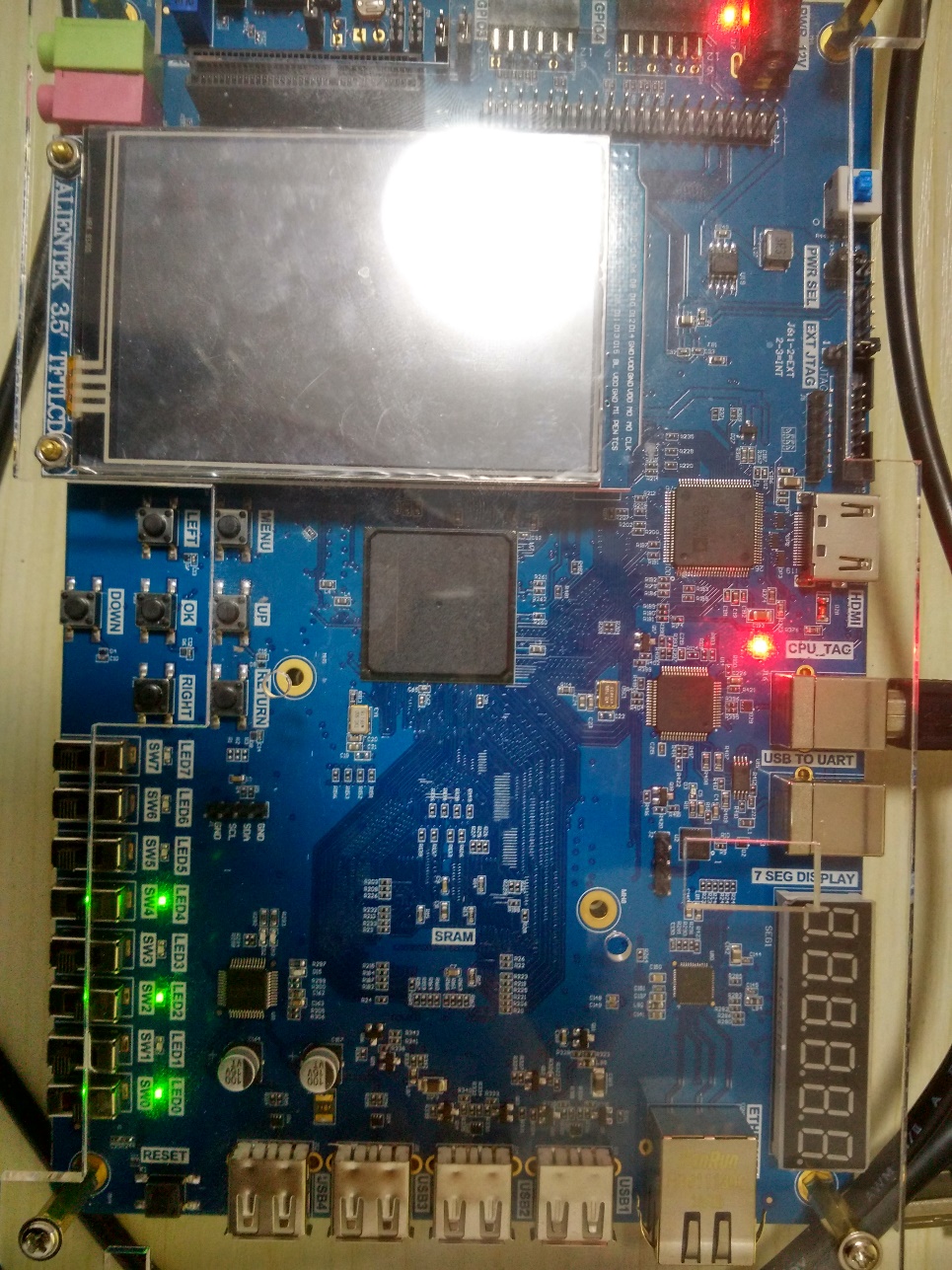

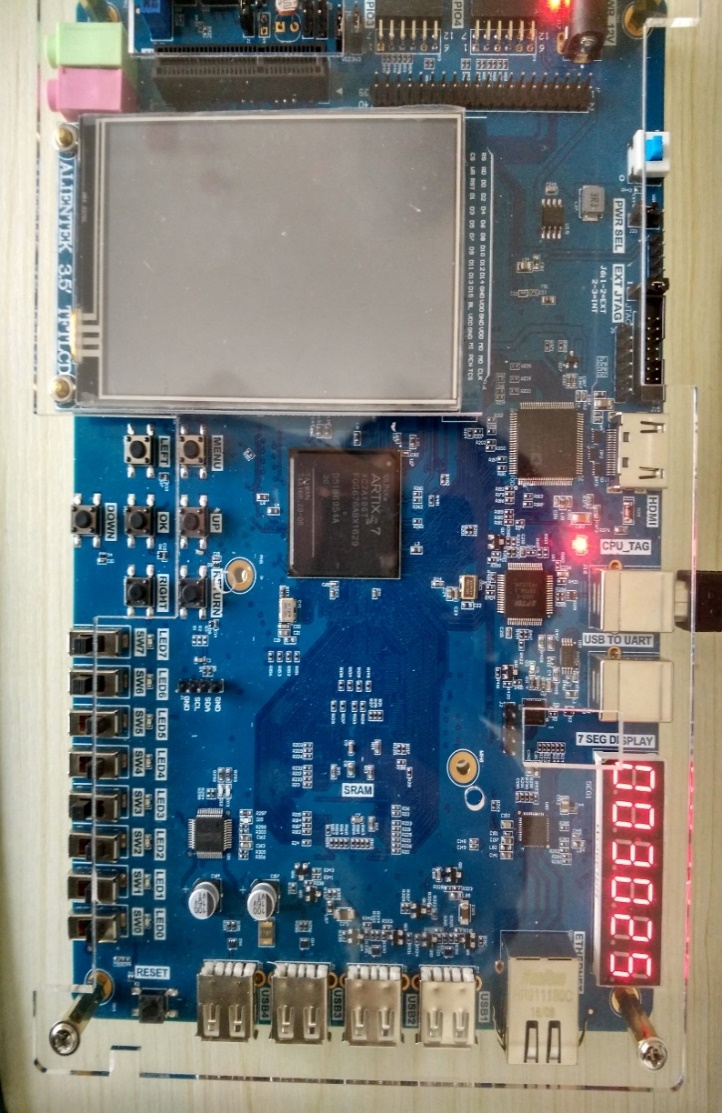

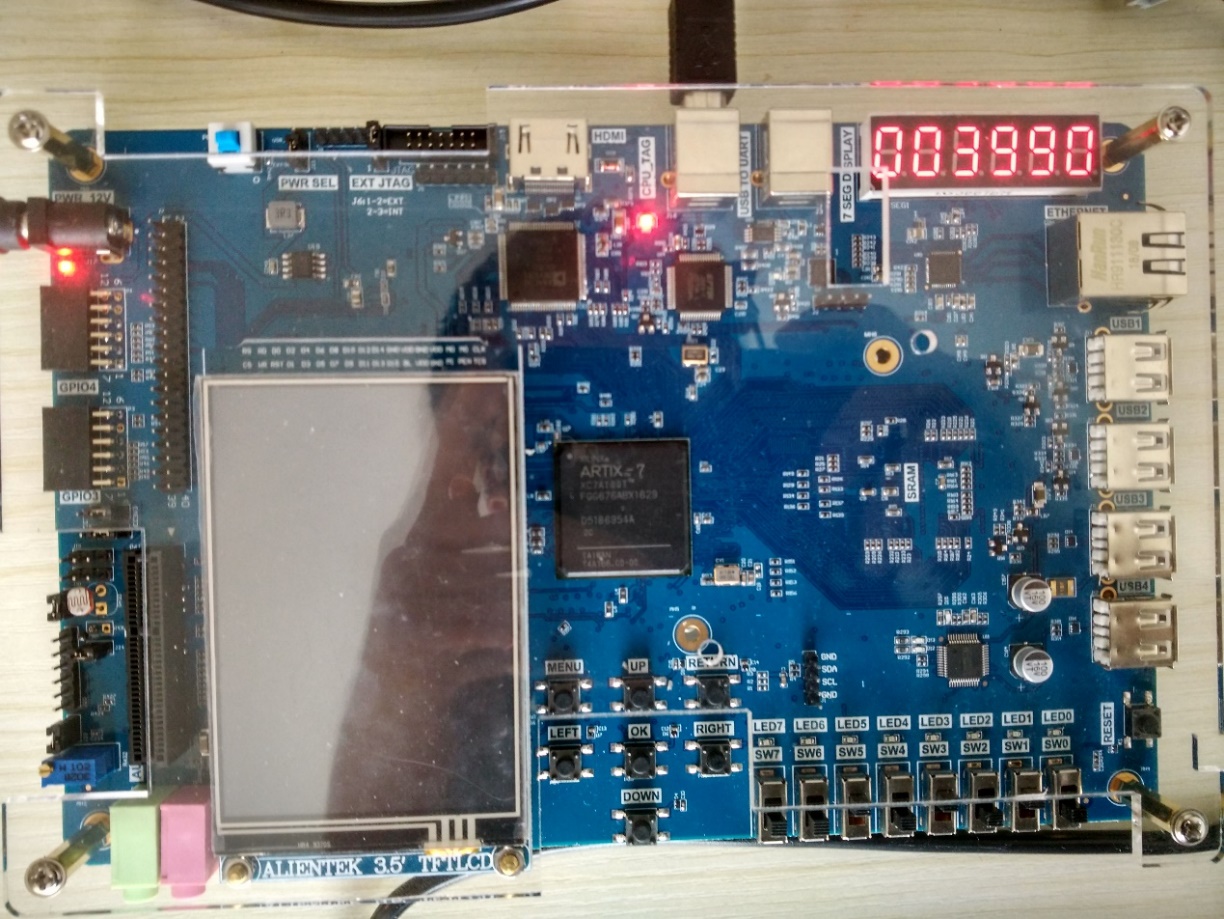

Experiment 11 Asynchronous Serial Port Design and Experiment 1.Experiment Objective Because asynchronous serial ports are very common in industrial control, communication, and software debugging, they are also vital in FPGA development. Learning the basic principles of asynchronous serial port communication, handshake mechanism, data frame Master asynchronous sampling techniques Review the frame structure of the data packet Learning FIFO Joint debugging with common debugging software of PC (SSCOM, teraterm, etc.) 2.Experiment Requirement Design and transmit full-duplex asynchronous communication interface Tx, Rx Baud rate of 11520 bps, 8-bit data, 1 start bit,…

Read More