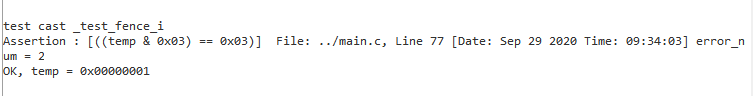

ASM Test Introduction

asm_test introduction document

V1.0

Fraser Innovation inc

asm_test introduction document

Version Control

| Version | Date | Description |

| 1.0 | 09/29/2020 | Initial Release |

Copyright Notice:

© 2020 Fraser Innovation Inc ALL RIGHTS RESERVED

Without written permission of Fraser Innovation Inc, no unit or individual may extract or modify part of or all the contents of this manual. Offenders will be held liable for their legal responsibility.

Thank you for purchasing the FPGA development board. Please read the manual carefully before using the product and make sure that you know how to use the product correctly. Improper operation may damage the development board. This manual is constantly updated, and it is recommended that you download the latest version when using.

Official Shopping Website:

Contents

1. Introduction 4

2. Test Projects 6

2.1)asm_test 6

2.2)jal_test 8

3. References 9

Introduction

asm_test hosts unit tests for different features of FII_RISC-V V3.01 processor. This CPU is fully pipelined and include irq feature. FII_RISC-V V3.01 include mul and div instructions. Its ROM write and read depth is set to be 16384 bits.

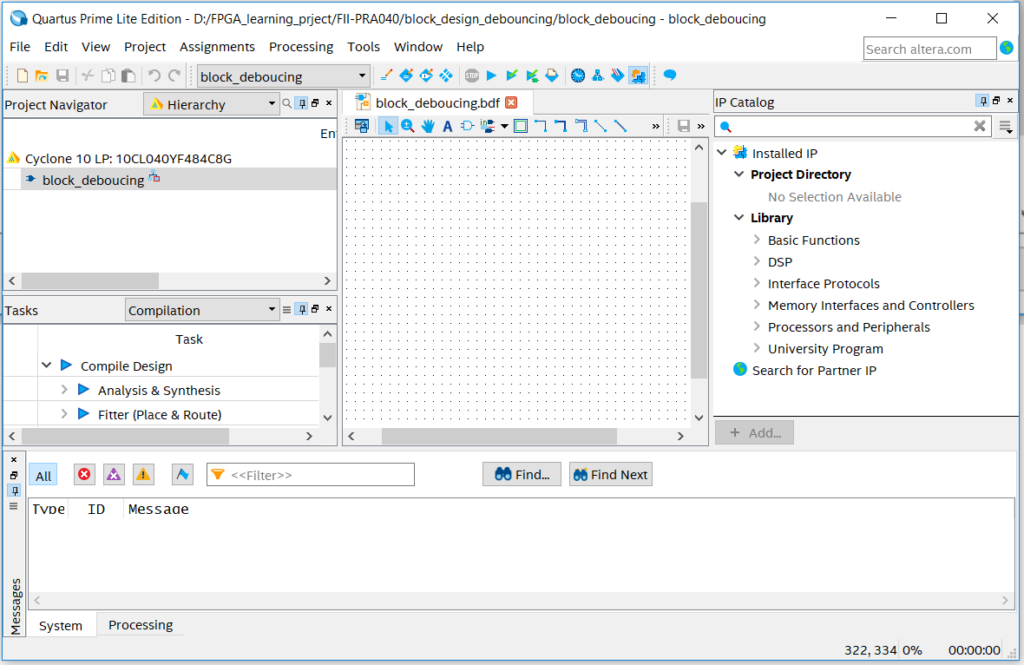

asm_test project contains test cases assembly files ,main file and header files for macros. It is build through FreedomStudio platform.asm_test will test all of the FII_RISC-V V3.01 processor supported instructions . The corresponding assembly files were stored in folder asm:

![]()

and listed below in Figure1.

Figure1 instruction test cases list

Basic Features

Each test case program should first include the riscv_test.h and test_macros.h header file, which defines the macros used by instruction assembly test file.

A test program for a RISC-V instruction is written within a single assembly language file, which is passed through the C preprocessor, and all regular assembly directives can be used.

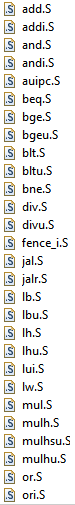

The test program will begin execution at the first instruction after defining the function name, and continue until execution reaches TEST_PASSFAIL macro or jalr t6, 0(t6) and then jump out from the current function. The testing result will be stored into register x26 and x27. if the result is implicitly a success, then 0x1 will be stored into x26 and x27. A test can explicitly fail by invoking the RVTEST_FAIL macro, and x27 will be set to 0x0. The related code is shown below in Figure2.

Figure2 code for RVTEST_PASS and RVTEST_FAIL

All user registers (pc, x0-x31, fsr) can be accessed inside test program, so the test case functions will store sp at the beginning of funtion and restore sp at the end of the function. The value of register ra is return address, so it will also be stored for returning to main program. The corresponding code is shown below in Figure3.

![]()

![]()

Figure3 store and restore code for register sp and ra

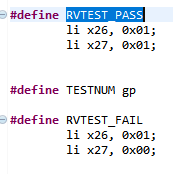

asm_test will print out the testing result of all instructions through serial port. The test result shows that all instructions except fence has passed the test, This is because FII_RISC-V V3.01 does not support fence instruction. Figure4 shows the error report for fence instruction.

Figure4 error report for fence instruction

2.2)jal_test

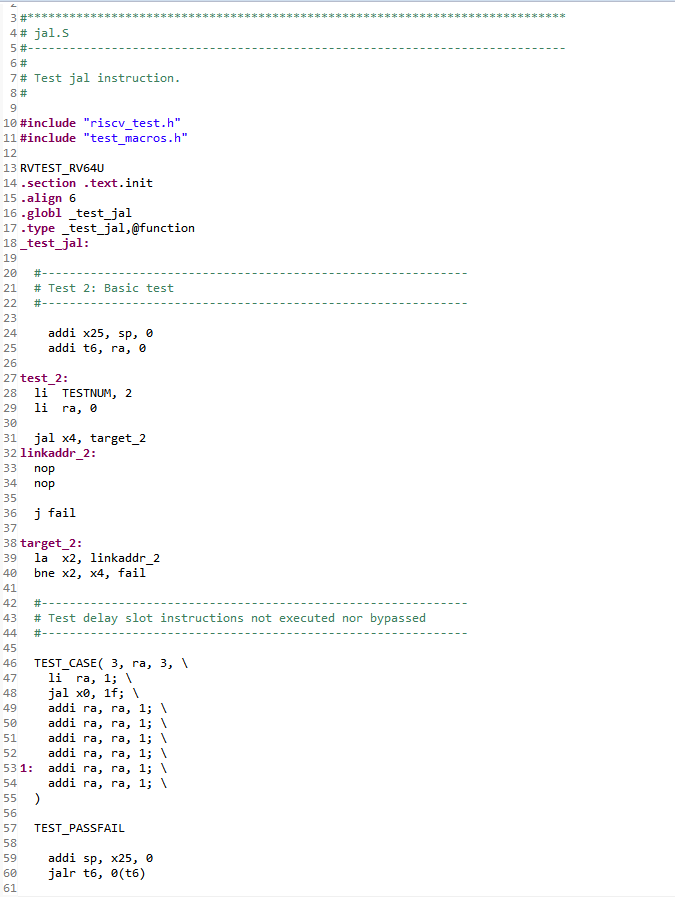

jal_test is a project which only runs an example test function _test_jal. The assembly code is shown in Figure 5.

Figure5 Test case for jal instruction

The example program contains self-checking code to test the result of jal instruction. A test can explicitly fail by invoking the RVTEST_FAIL macro, and it will continue run inside infinite loop called loop fail. The corresponding code is shown below in Figure6.

References

- https://github.com/riscv/riscv-tests