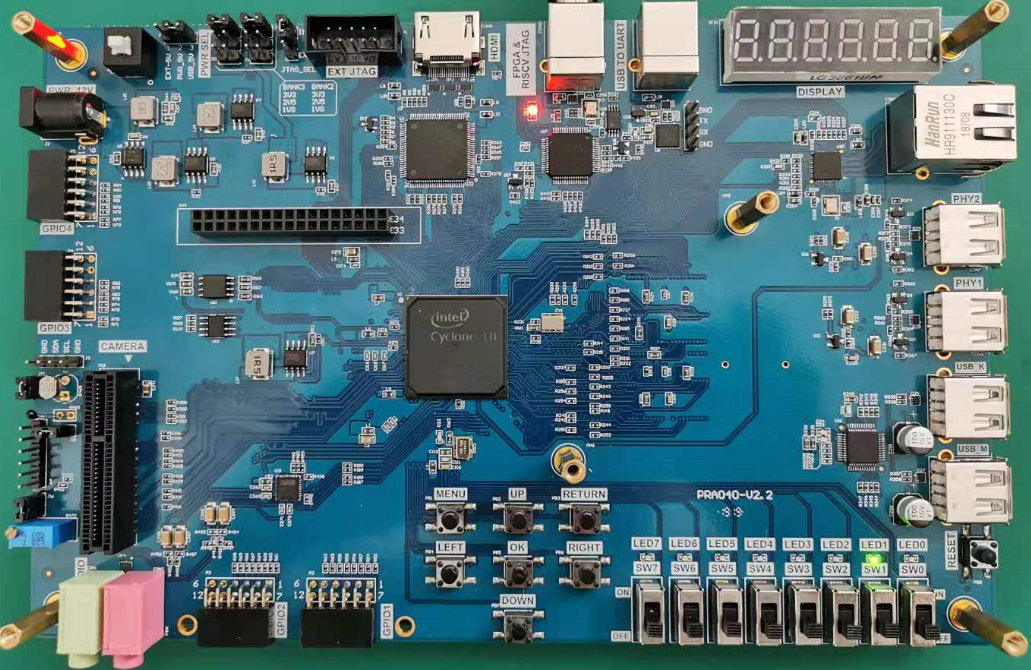

Altera Risc-V FPGA Tutorial : Use of ROM – Study the format of *.mif and how to edit *.mif file,Learn to use RAM, read and write RAM, FII-PRA040 FPGA Board Experimental 8

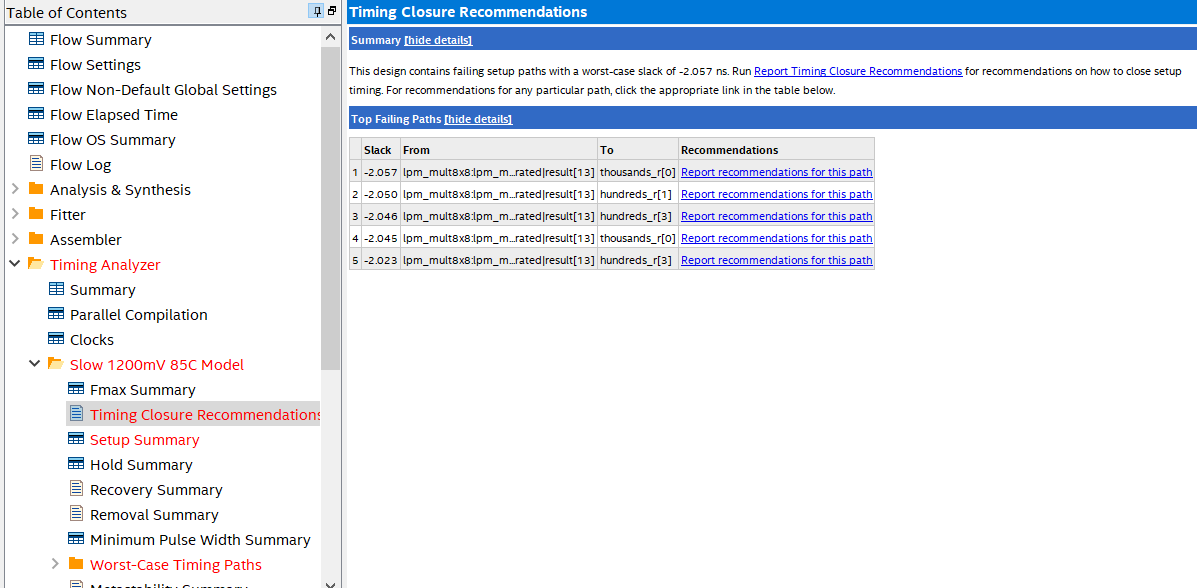

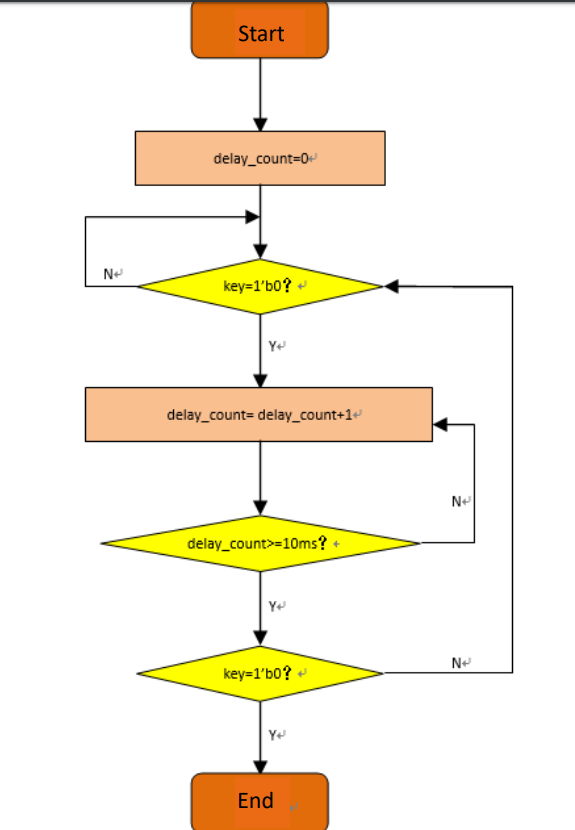

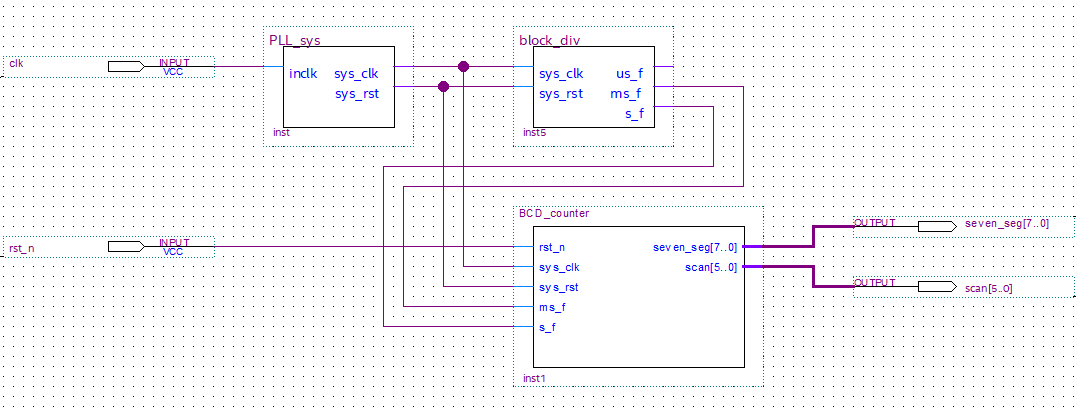

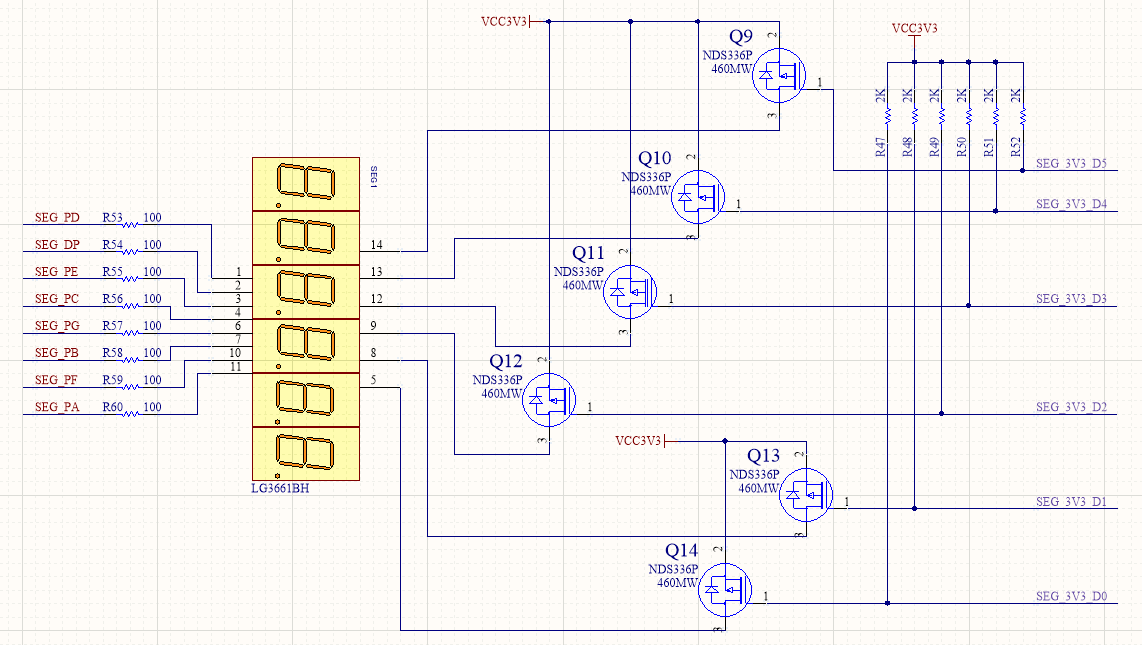

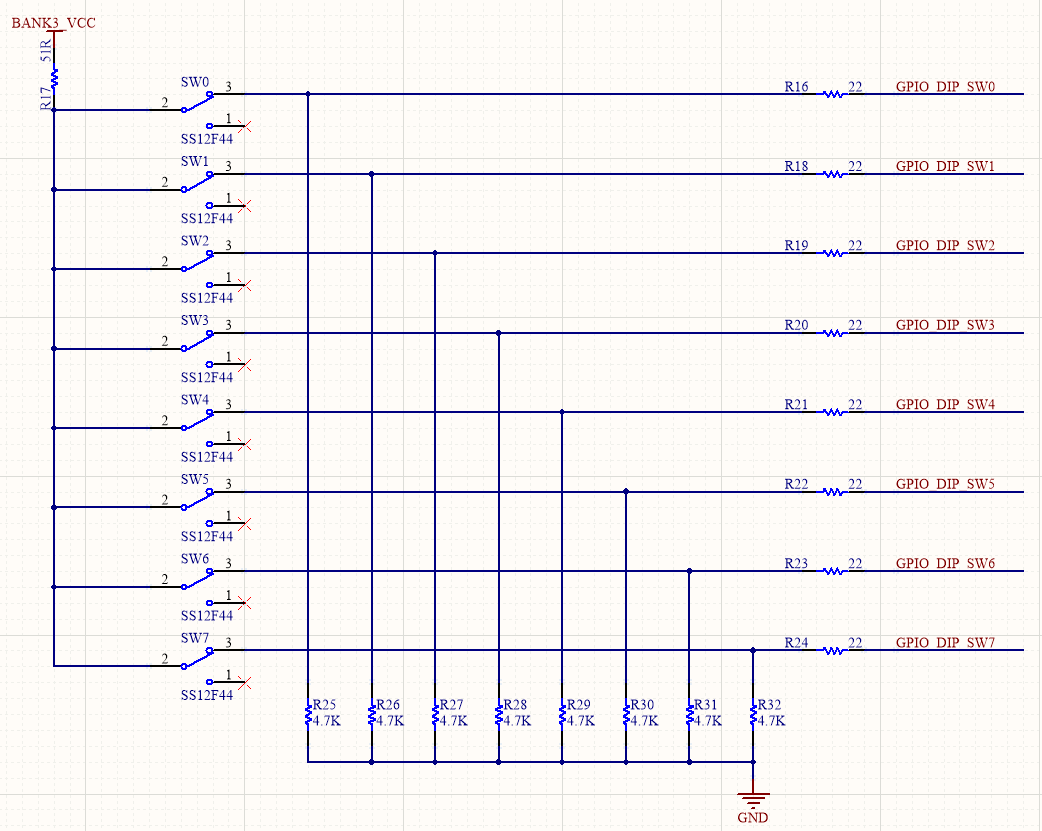

Experiment 8 Use of ROM 8.1 Experiment Objective Study the internal memory block of FPGA Study the format of *.mif and how to edit *.mif file to configure the contents of ROM Learn to use RAM, read and write RAM 8.2 Experiment Implement Design 16 outputs ROM, address ranging 0-255 Interface 8-bit switch input as ROM’s address Segment display the contents of ROM and require conversion of hexadecimal to BCD output. 8.3 Experiment 8.3.1 Introduction of the Program This experiment was carried out on the basis of Experiment 7, and…

Read More