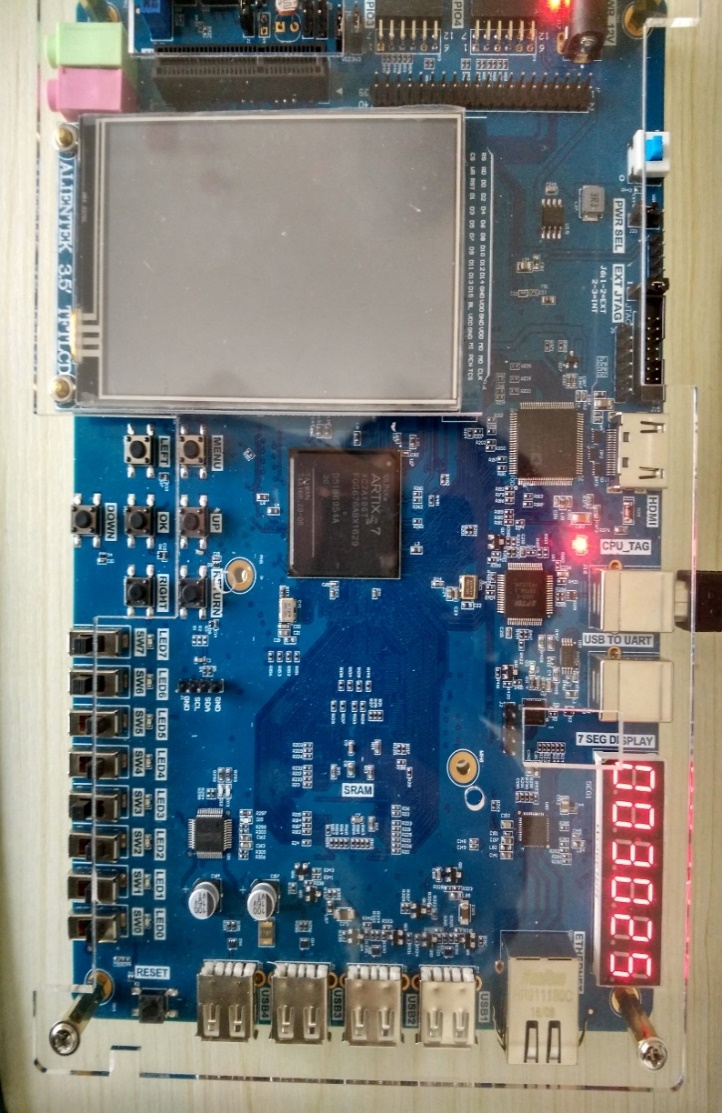

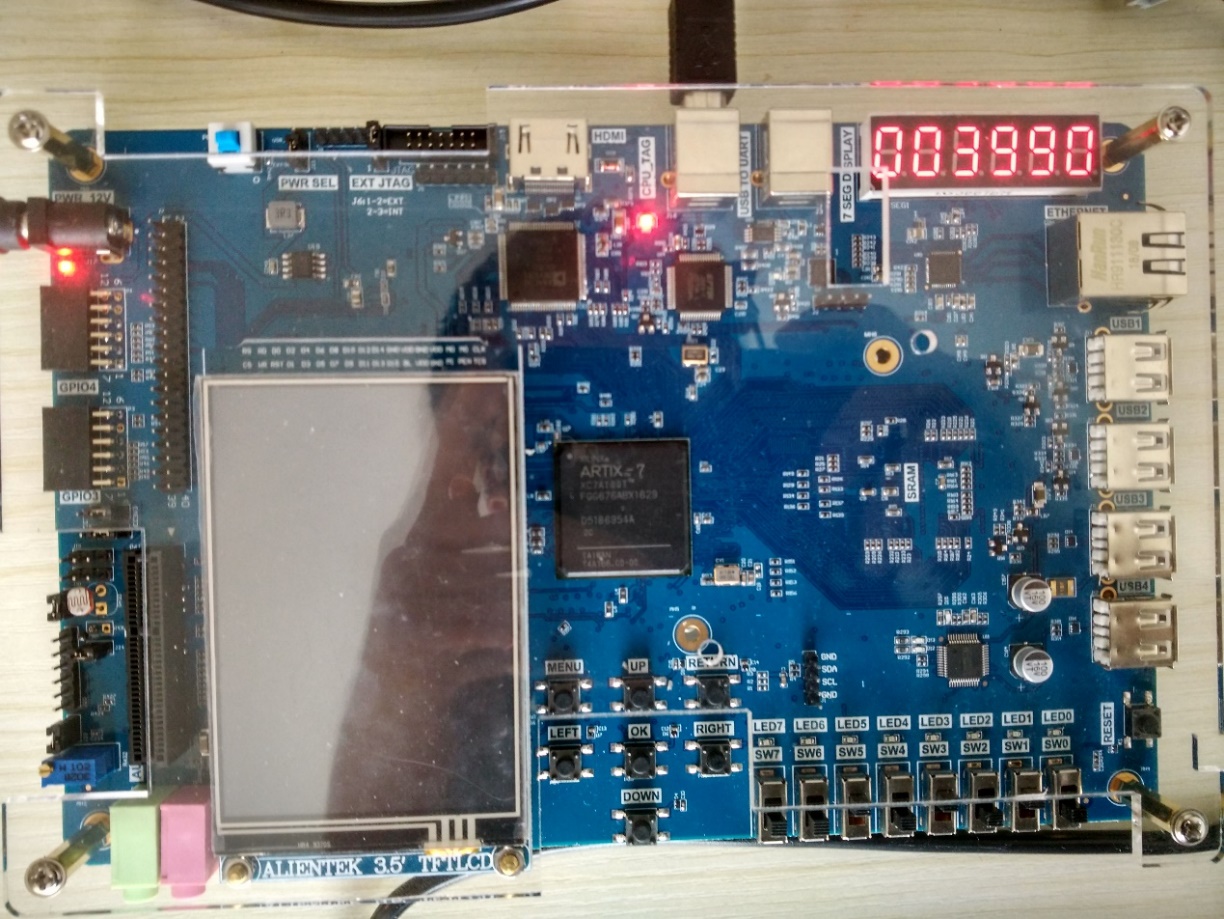

SOPC (NiosII) system, simulation and verification of RISC-V CPU, Basic FPGA design training, IC design and verification – Altera Risc-V Board Tutorial : Introduction of FII-PRA040 Development System

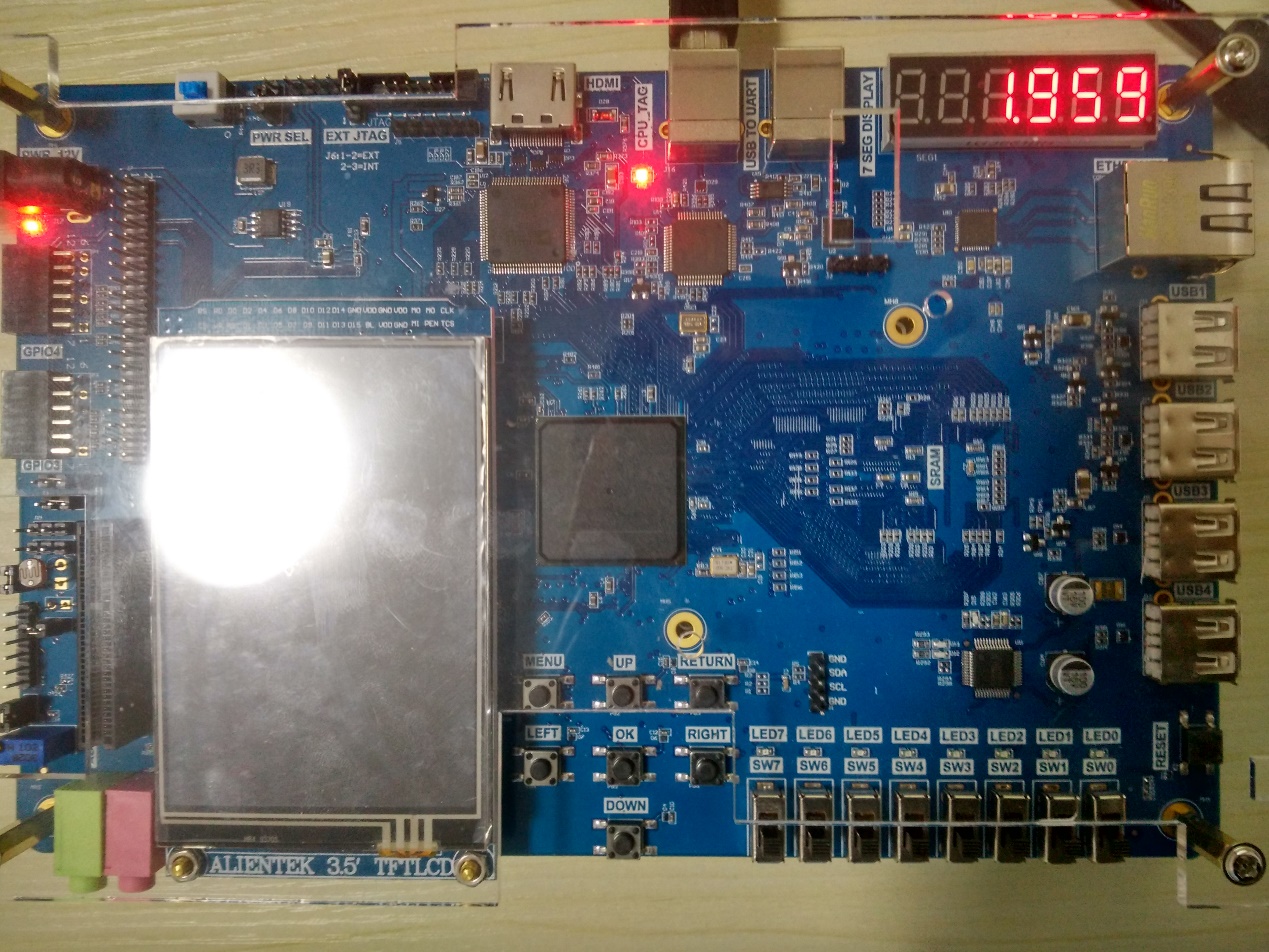

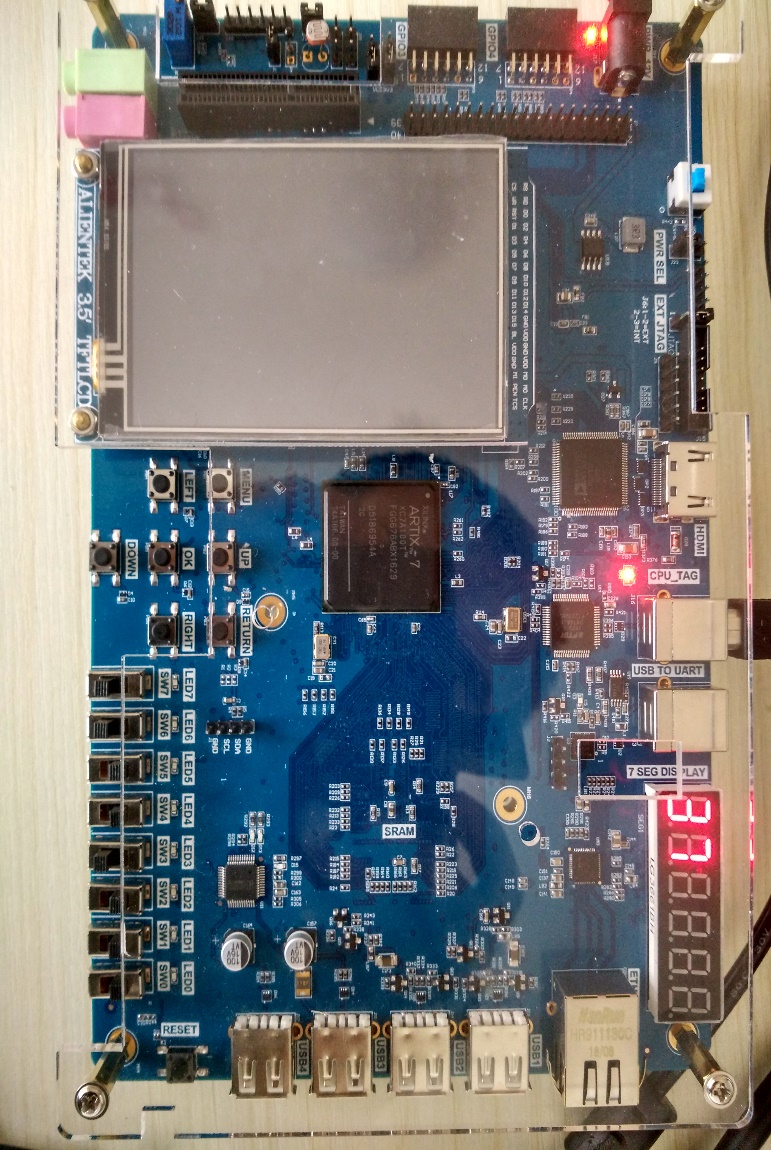

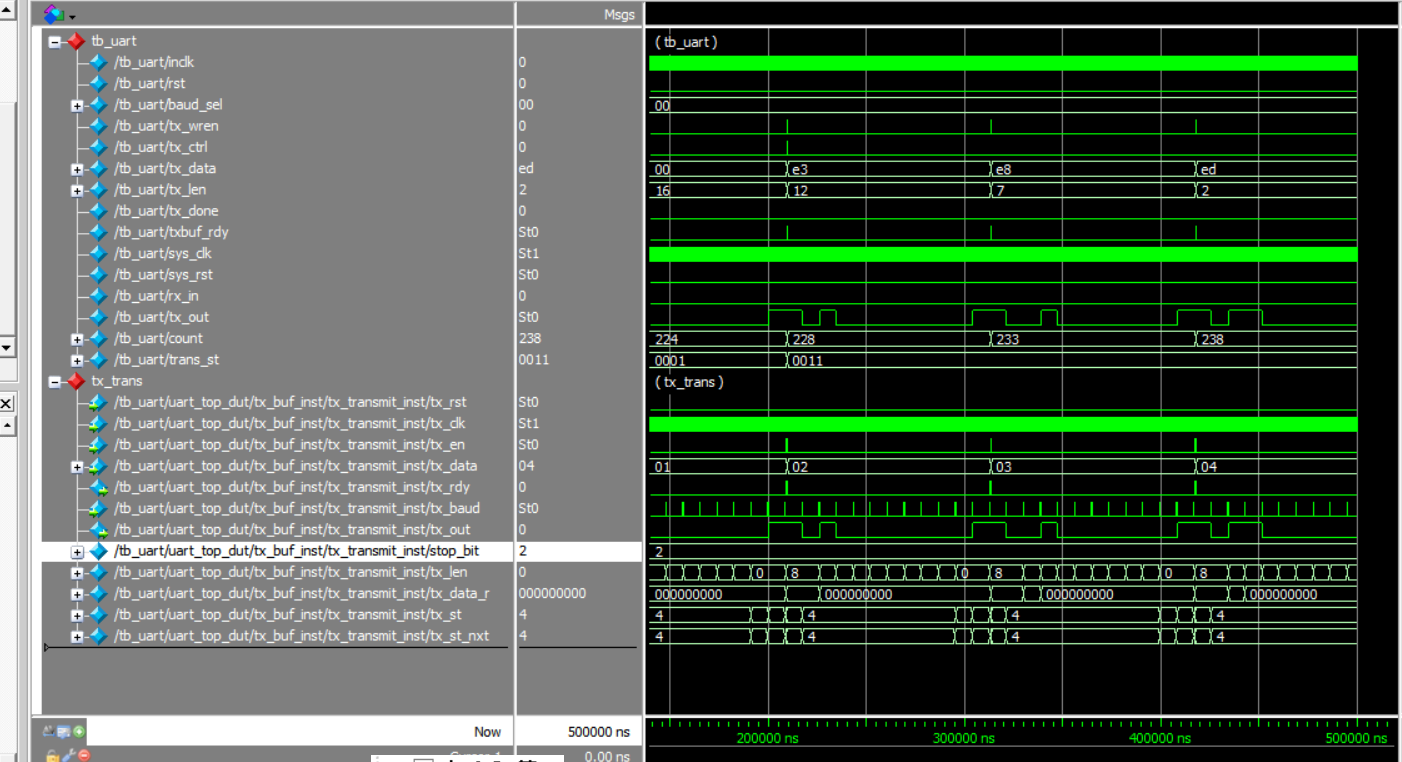

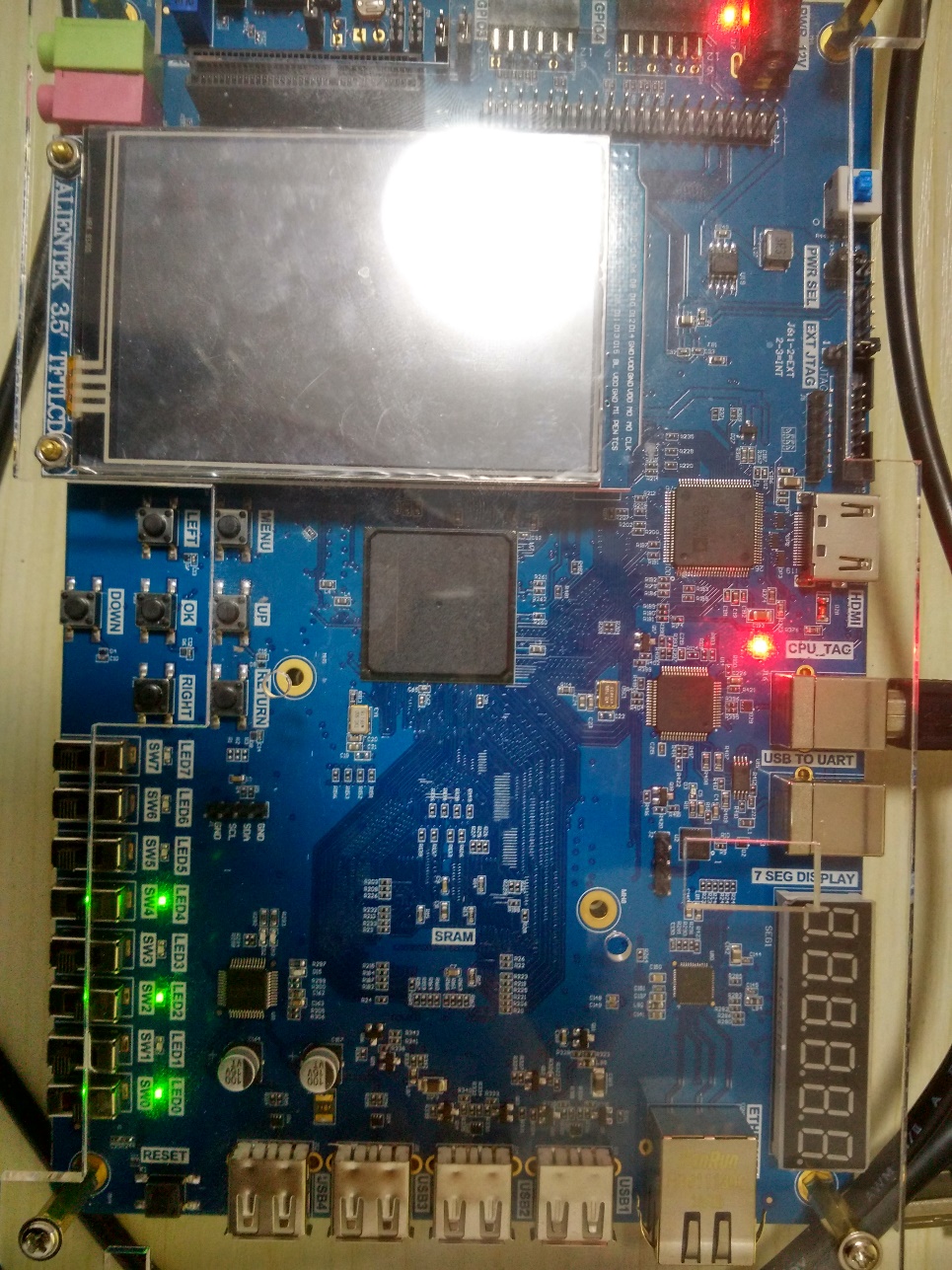

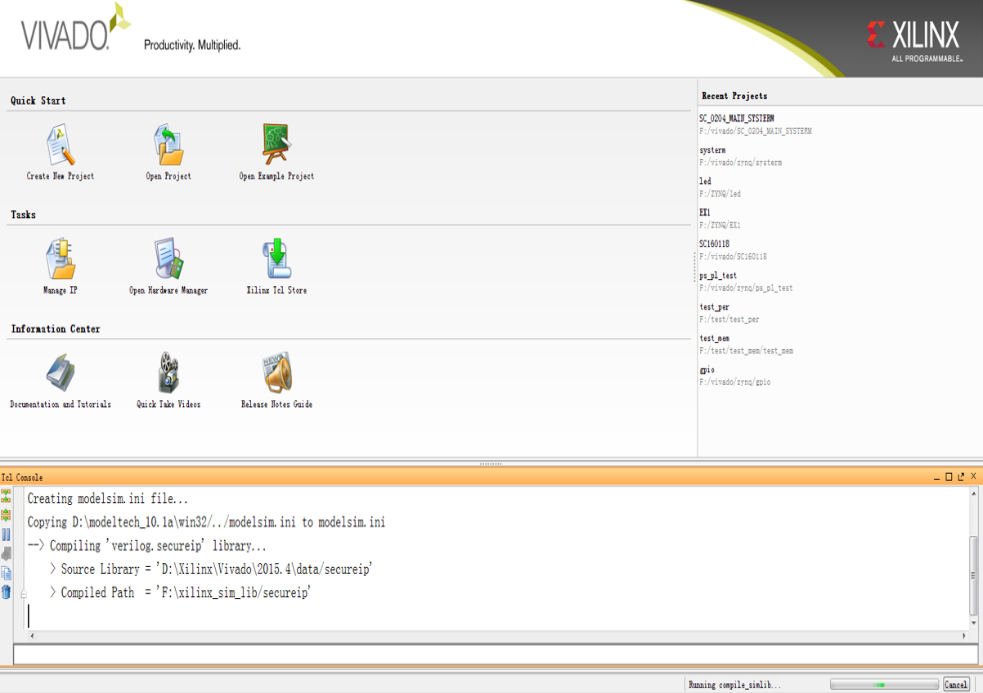

1、Design Objective of the System The main purpose of this system design is to complete FPGA learning, development and experiment with Intel Quartus. The main device uses the Inte Cyclone10 10CL040YF484C8G and is currently the latest generation of FPGA devices from Intel. The major learning and development projects can be completed as follows: Basic FPGA design training Construction and training of the SOPC (NiosII) system IC design and verification, the system provides hardware design, simulation and verification of RISC-V CPU Development and application based on RISC-V The system is specifically…

Read More