Reading Experiment of Serial Port Partition of Static Memory SRAM, Read and write timing of IS61WV25616BLL SRAM, and prepare for the next experimental experiment of OV5640 camera experiment – – Xilinx Risc-V FII-PRX100 Board Experiment 17

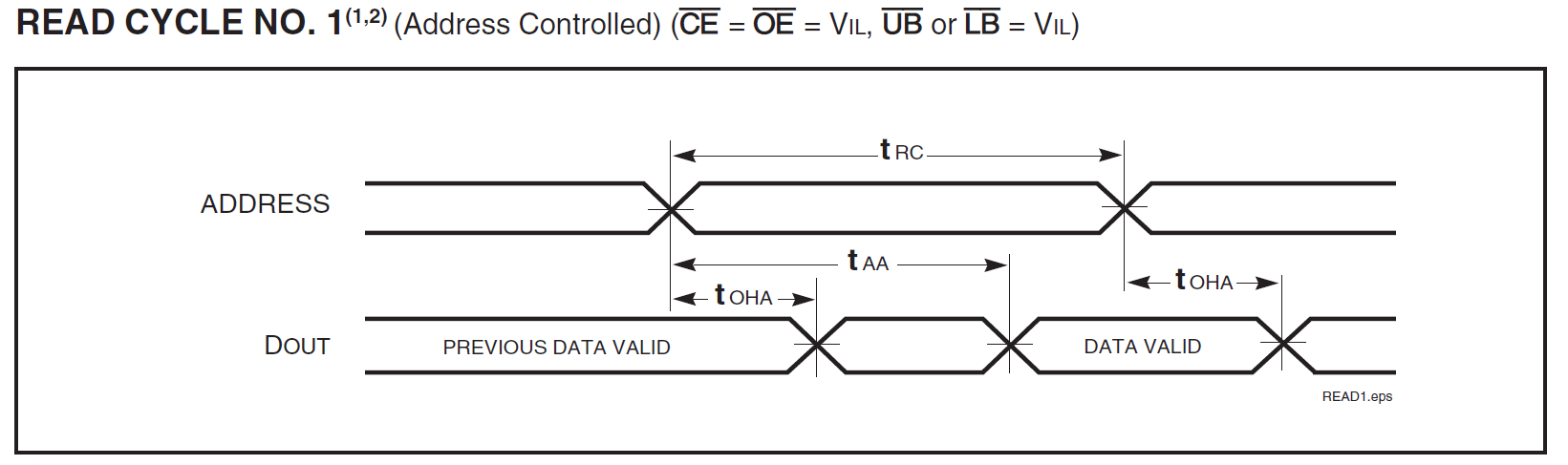

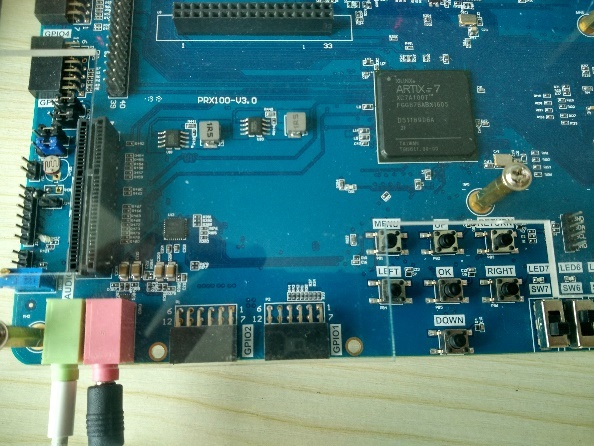

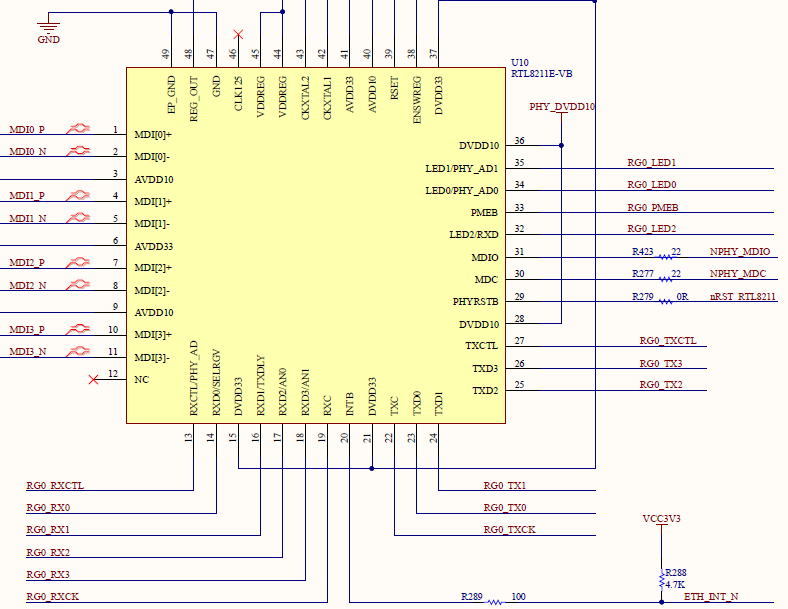

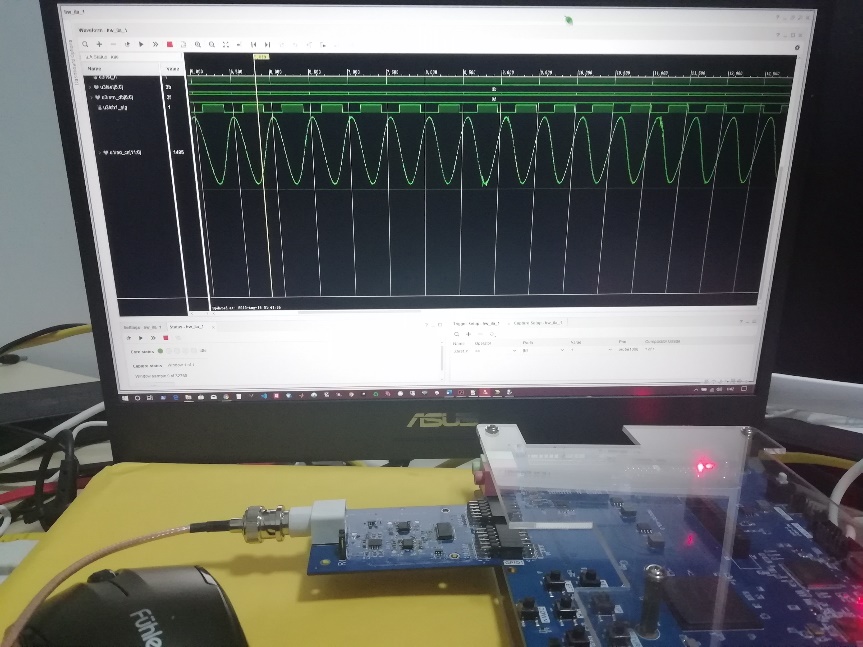

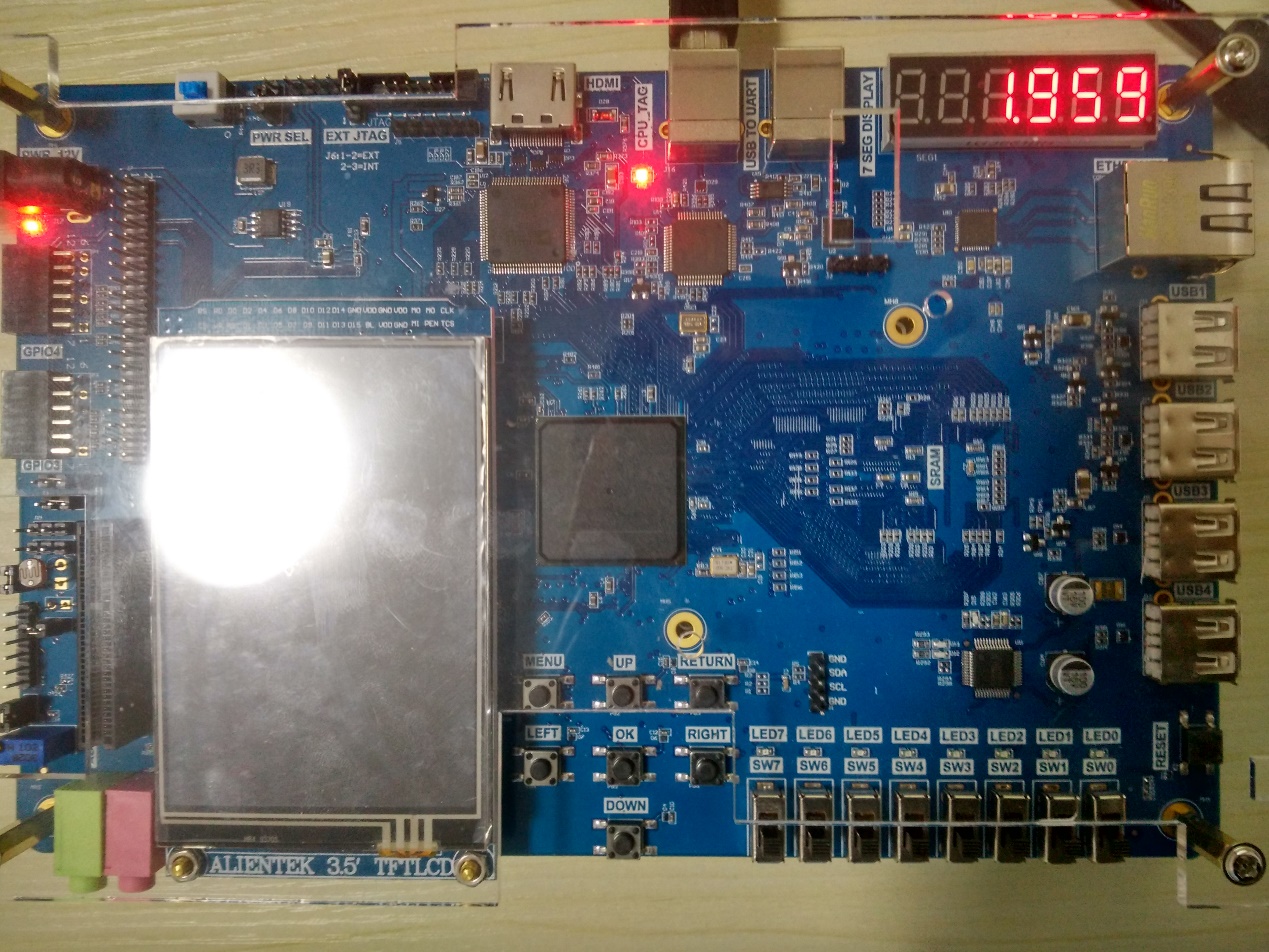

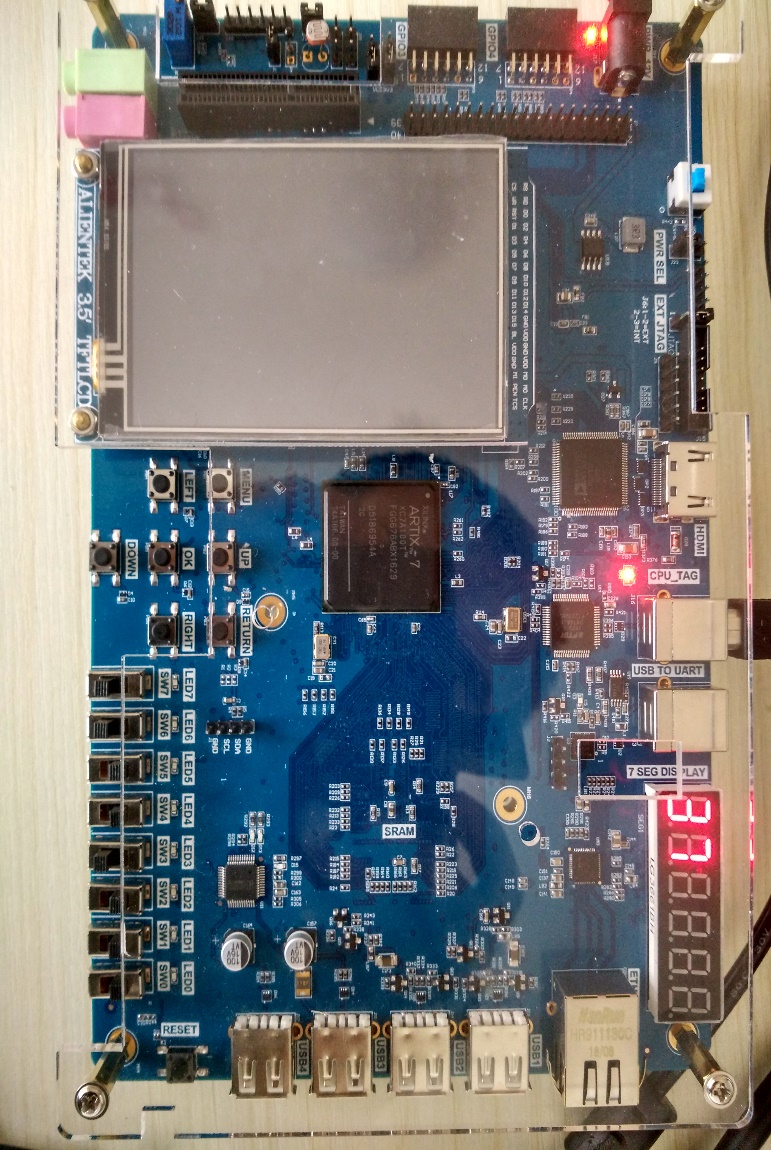

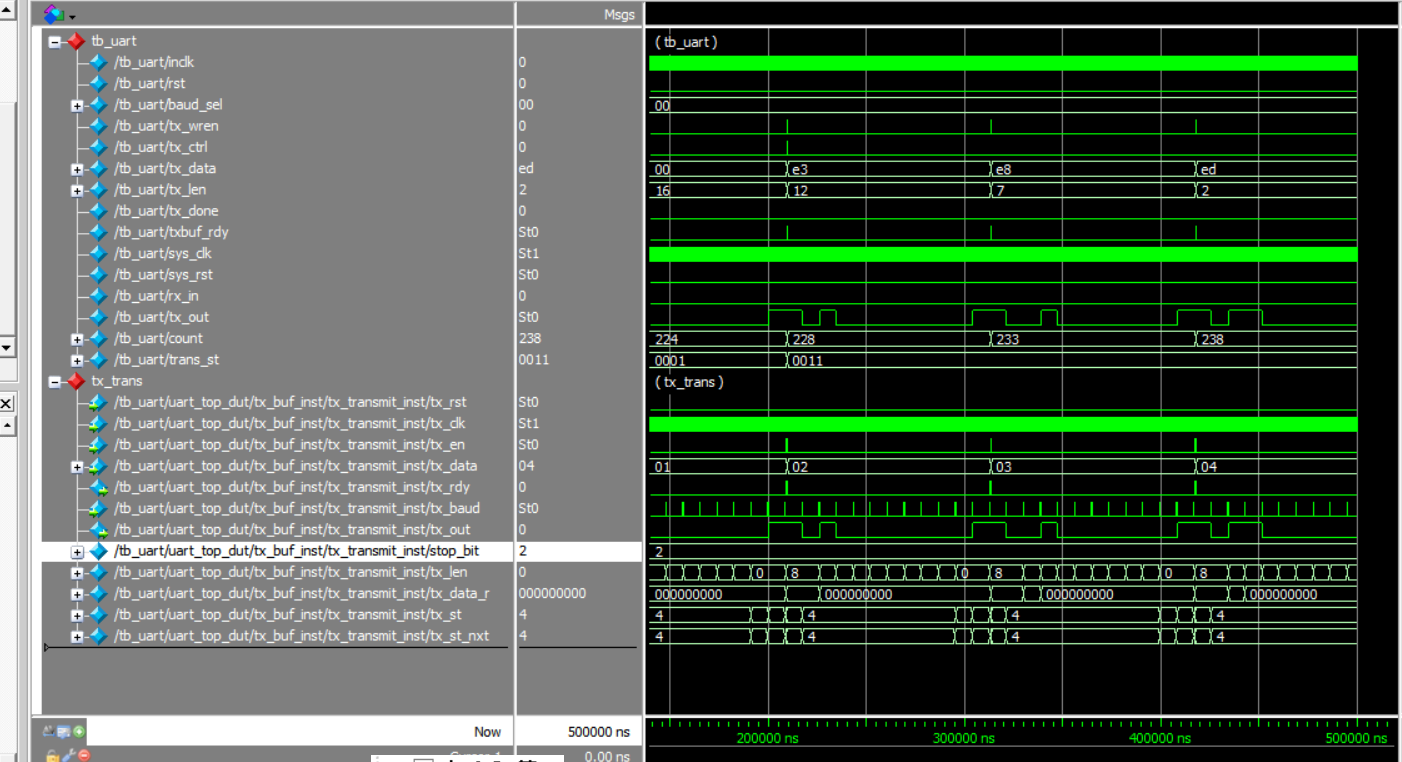

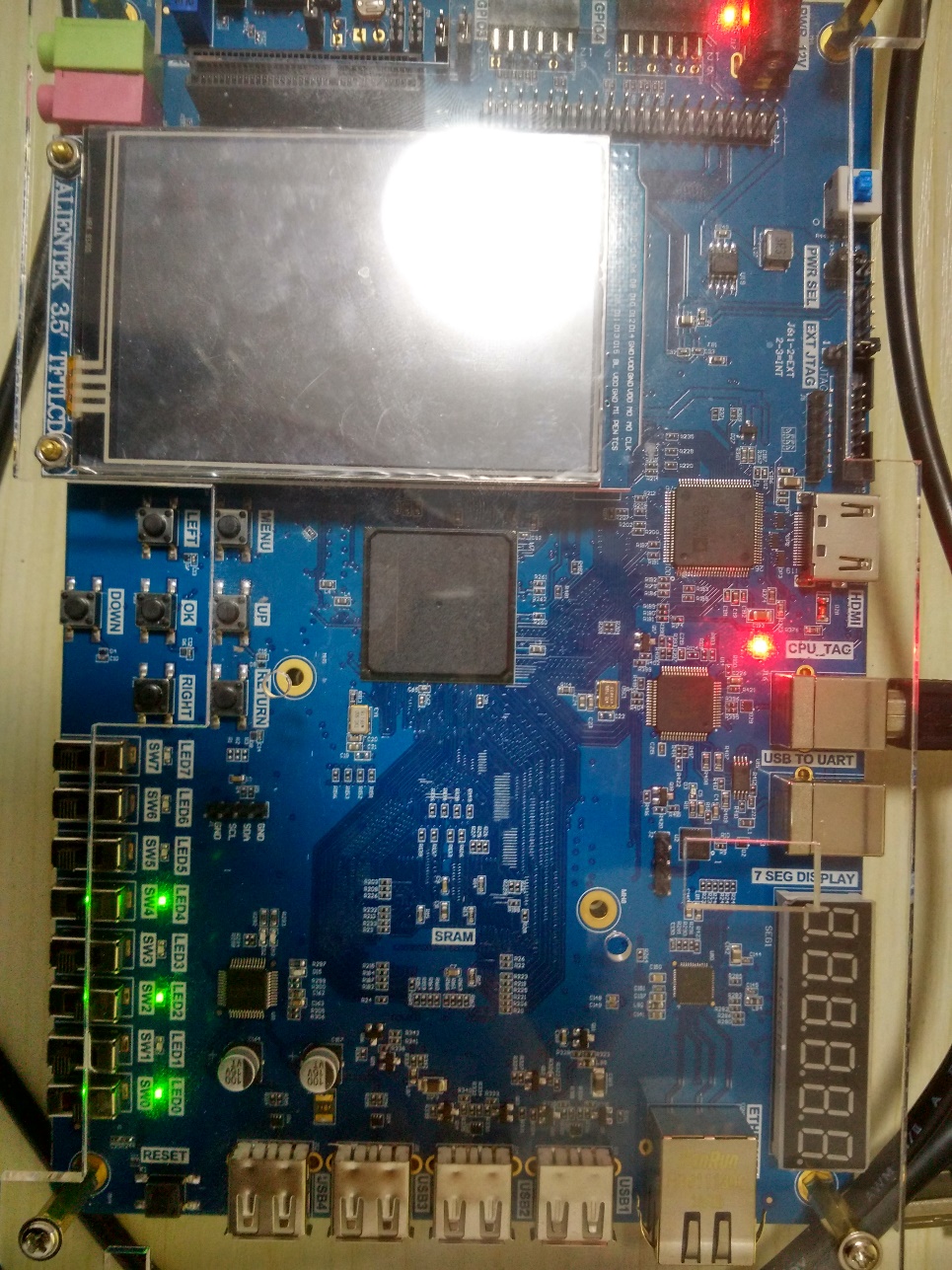

Experiment 17 Reading Experiment of Serial Port Partition of Static Memory SRAM 17.1 Experiment Objective Learn about static memory SRAM read and write operations and how it works Familiar with the read and write timing of IS61WV25616BLL SRAM, and prepare for the next experimental experiment of OV5640 camera experiment. 17.2 Experiment Implement The experimental board is equipped with two pieces of SRAM, which are combined to form 18-bit address lines and 32-bit data spaces. After power-on, the FPGA will write the same value in the corresponding address in the entire…

Read More