Study the internal memory block of FPGA, Study the format of *.mif and how to edit *.mif file to configure the contents of ROM : Use of ROM – FII-PRX100 Risc-V FPGA Board Experiment 9

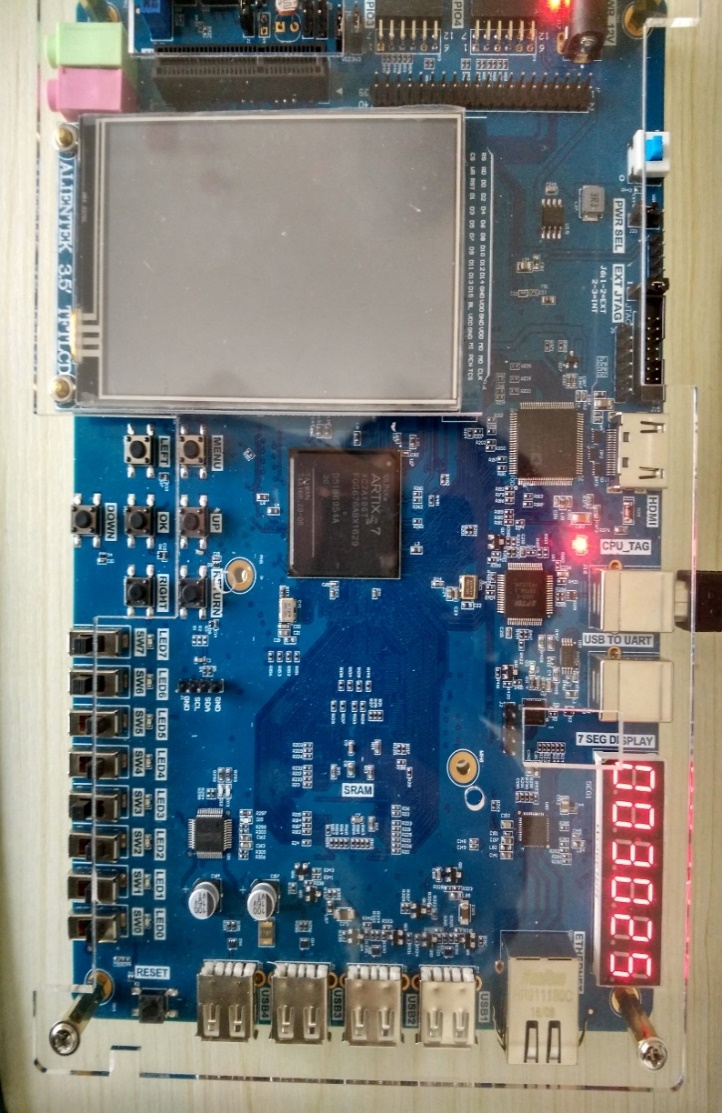

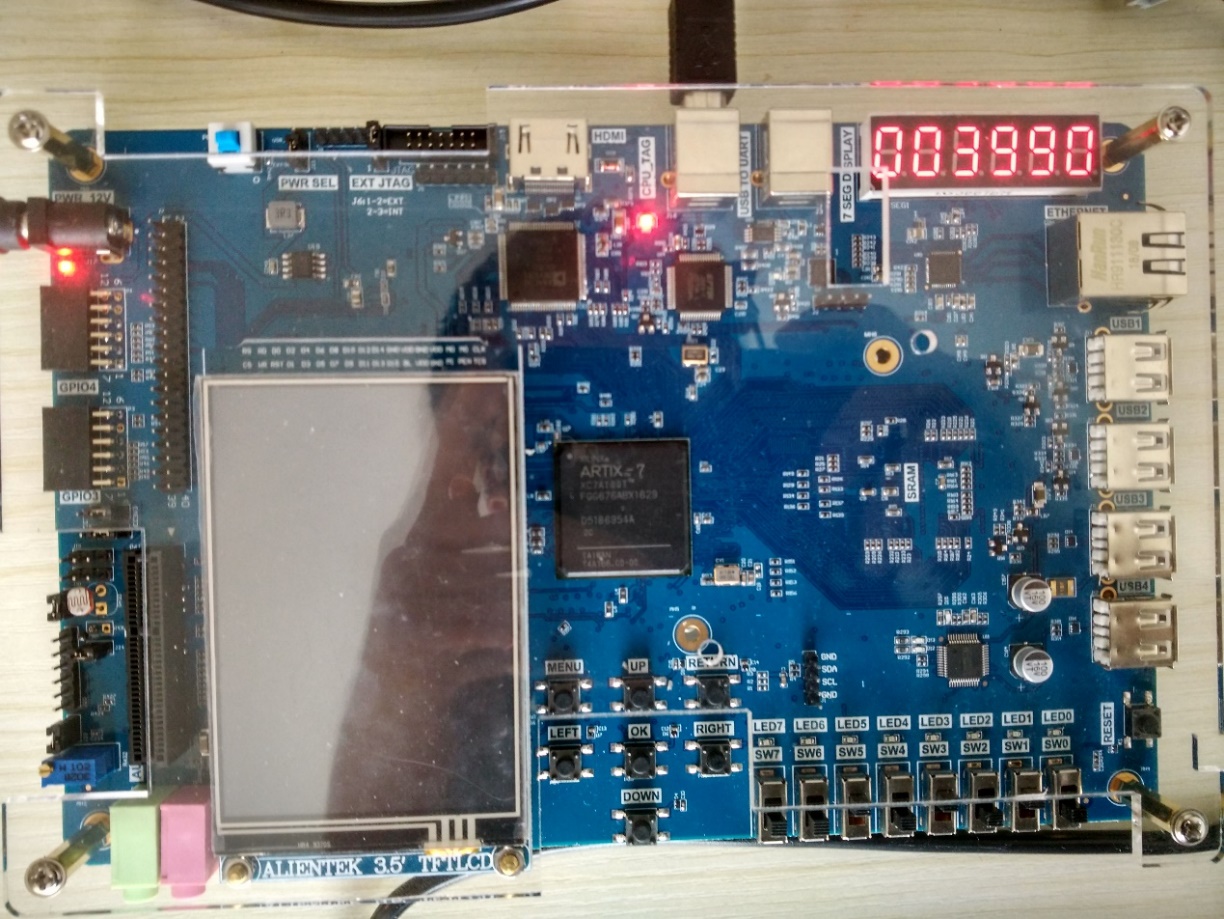

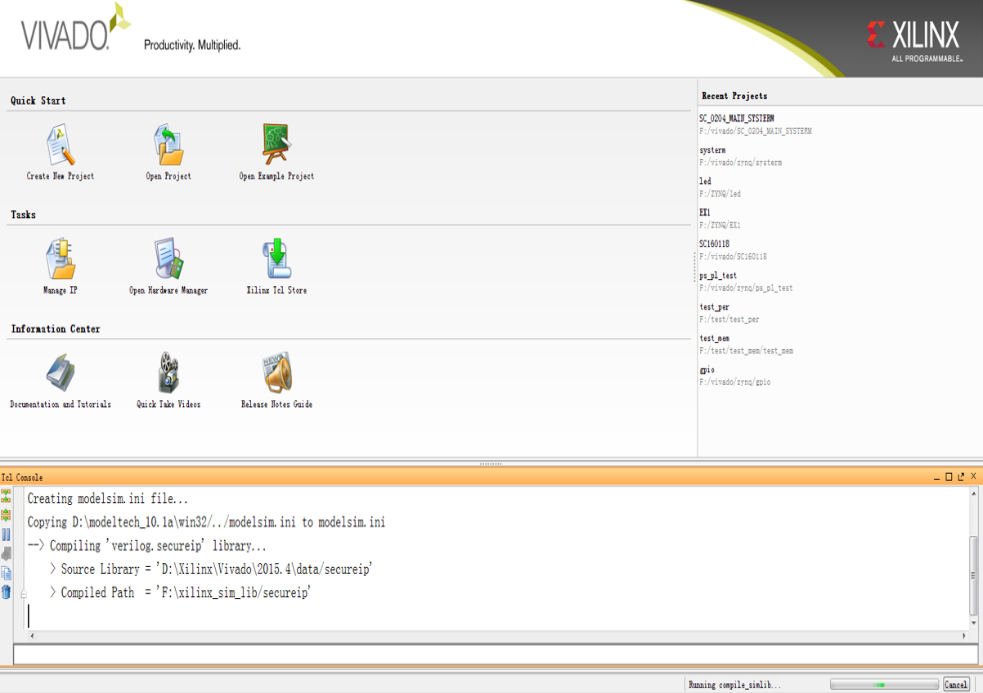

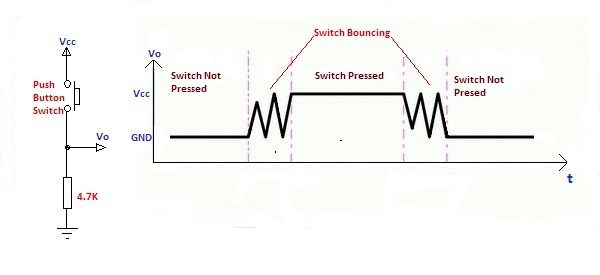

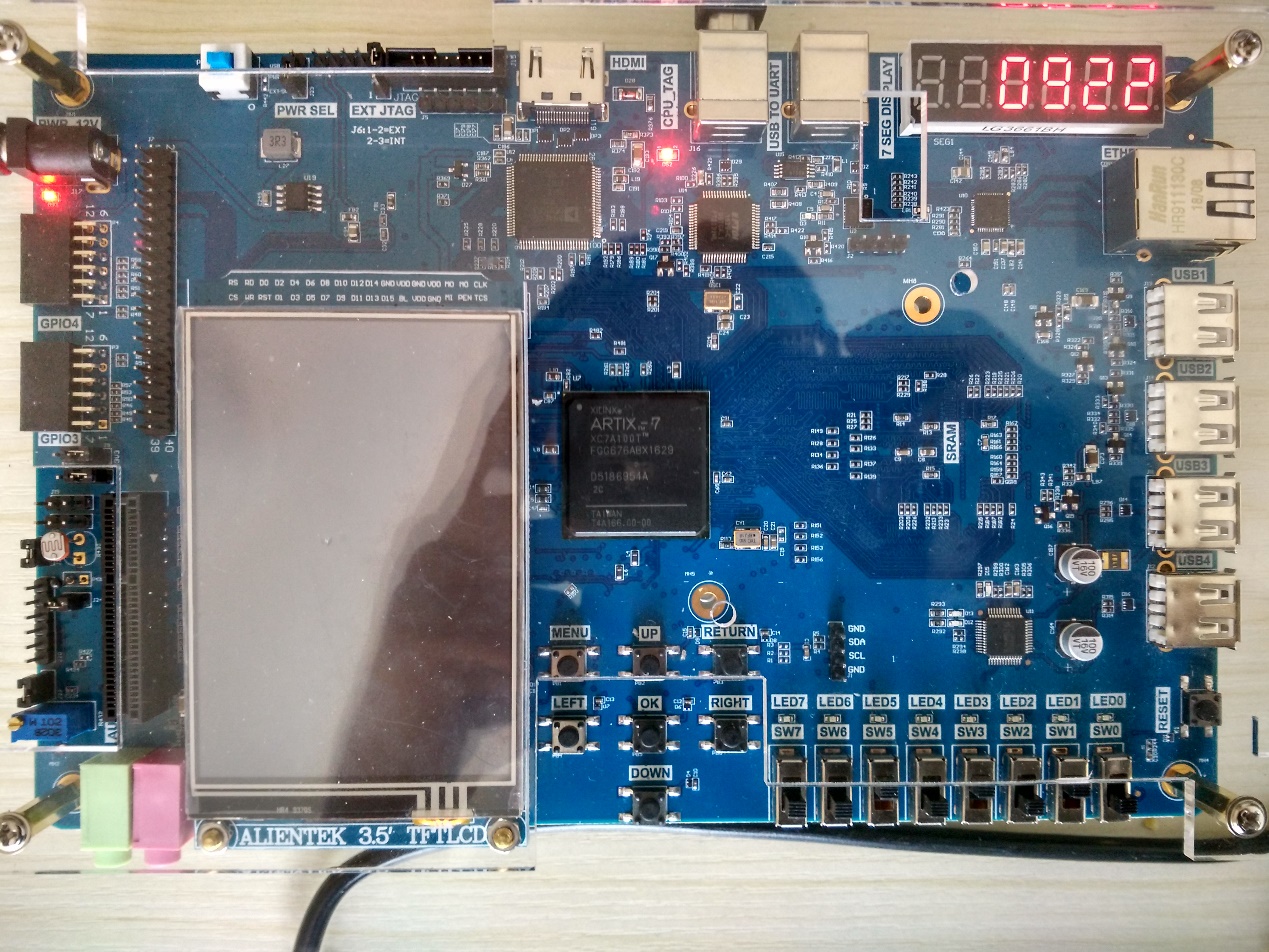

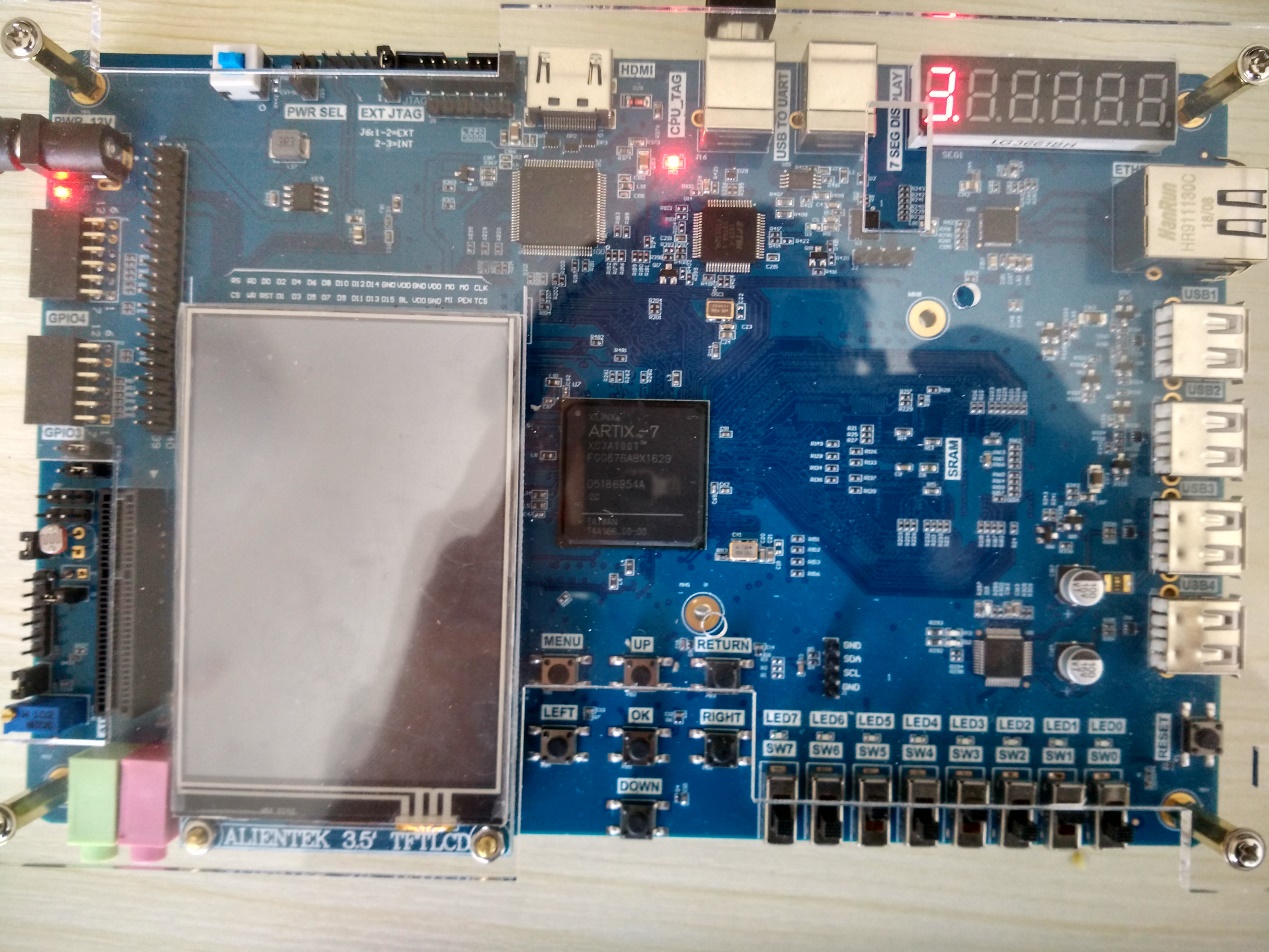

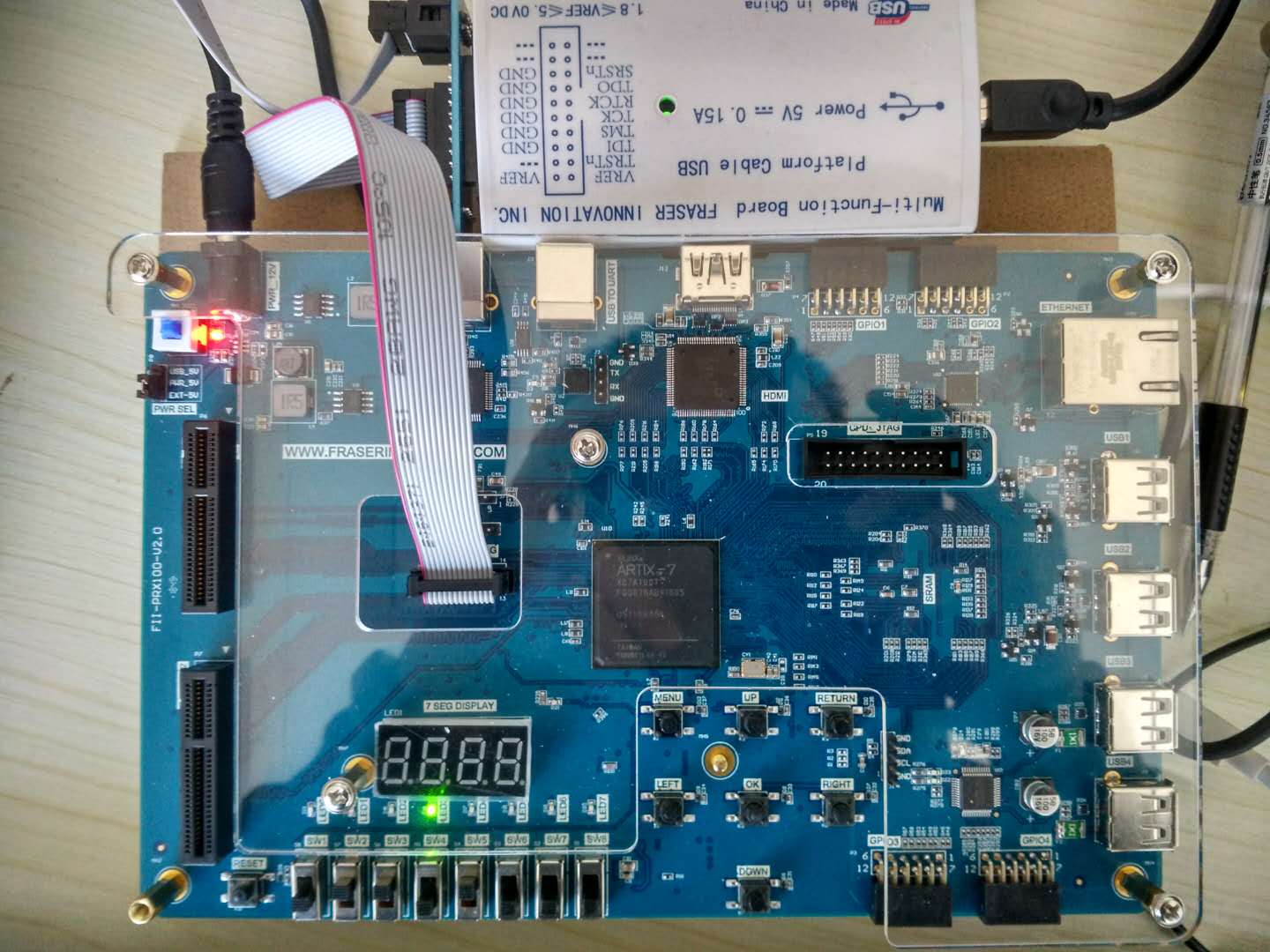

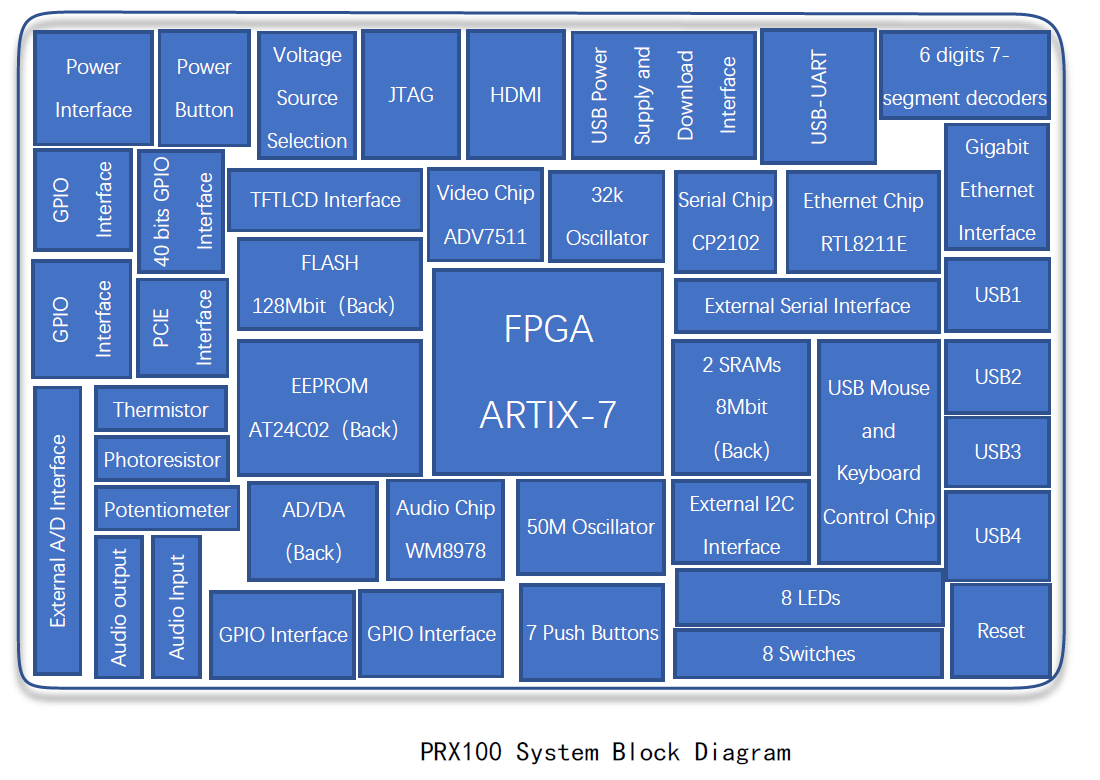

Experiment 9 Use of ROM 1.Experiment Objective Study the internal memory block of FPGA Study the format of *.mif and how to edit *.mif file to configure the contents of ROM Learn to use RAM, read and write RAM 2.Experiment Design Design 16 outputs ROM, address ranging 0-255 Interface 8-bit switch input as ROM’s address Segment decoders display the contents of ROM and require conversion of hexadecimal to BCD output. 3.Design Procedure Create a coe file. This experiment *.coe file is generated based on Matlab2018. The *.m file is as…

Read More