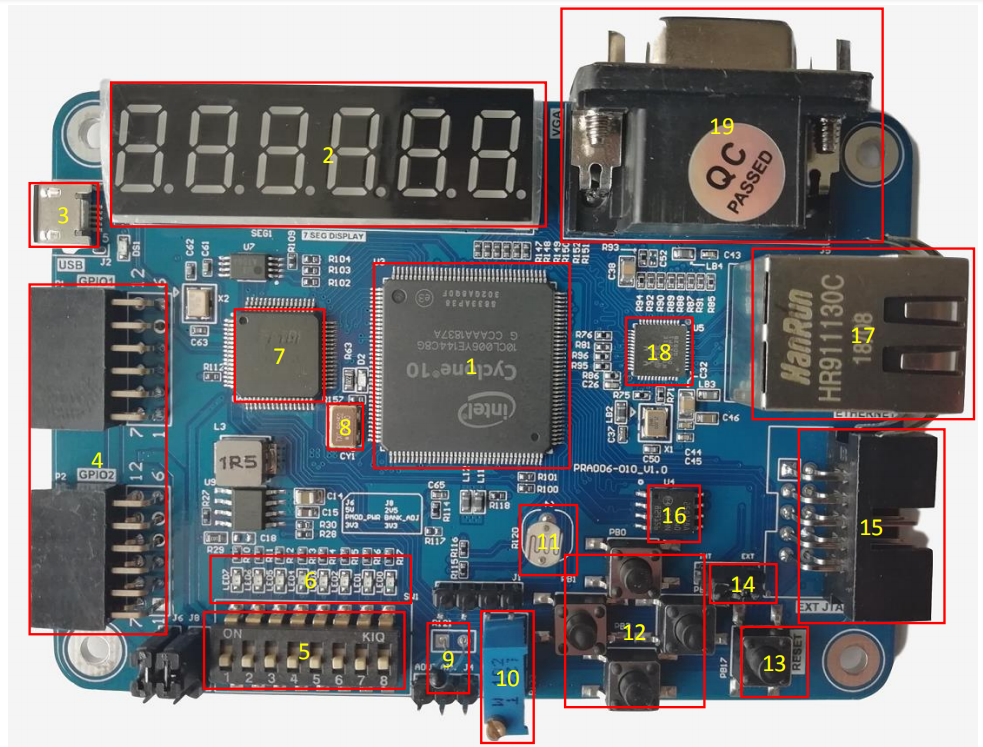

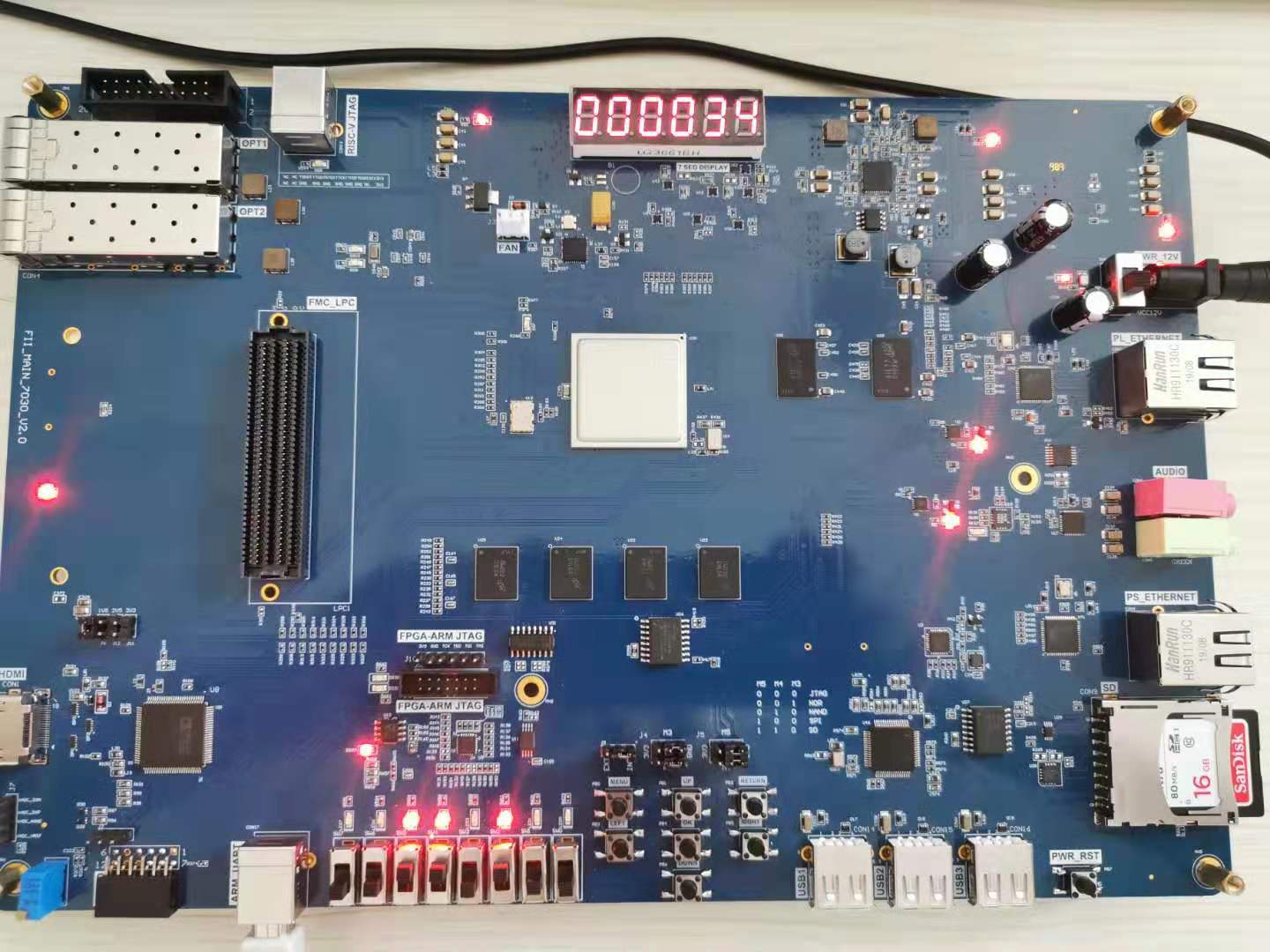

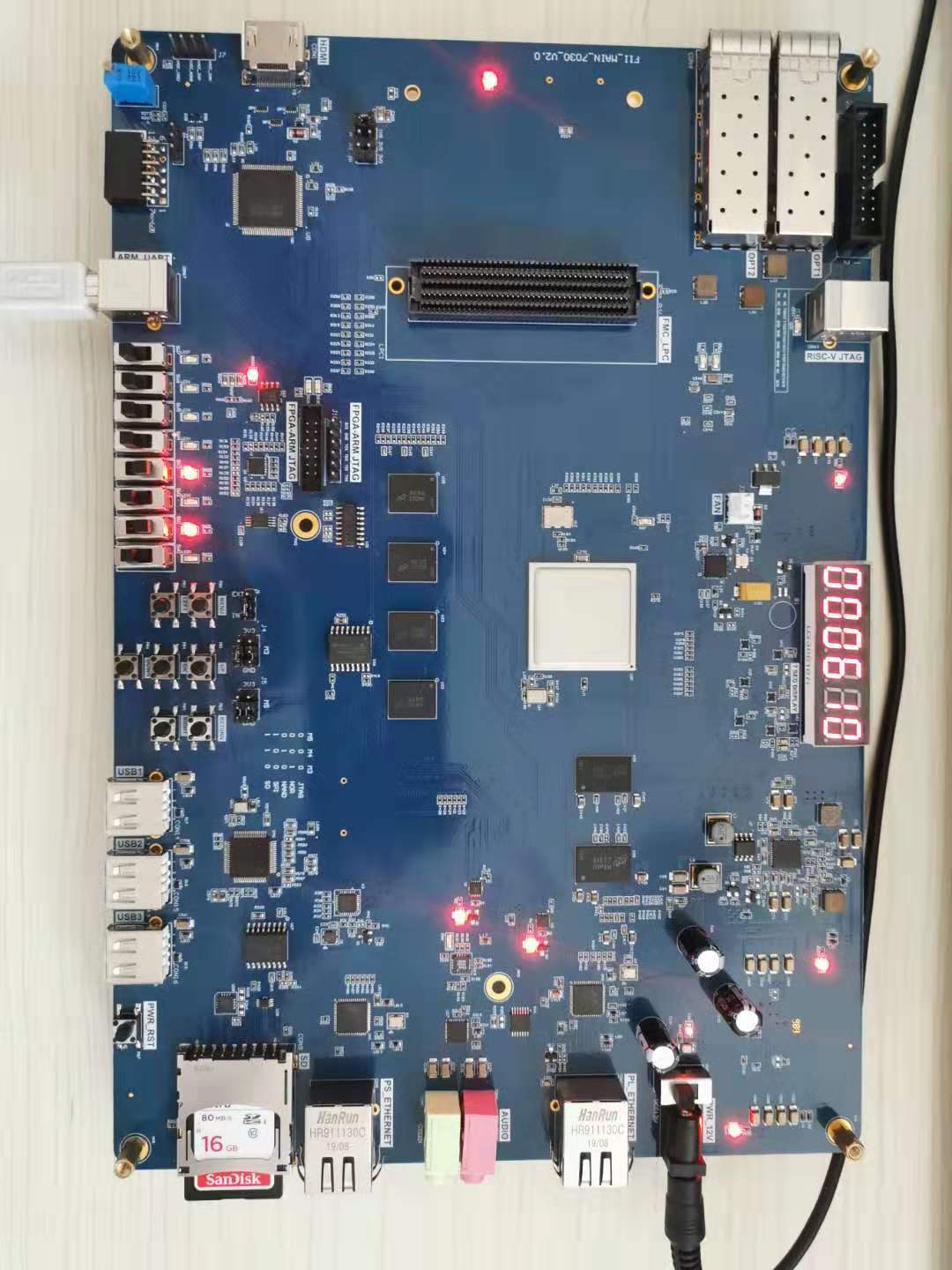

xc7z030 board hardware resources and block diagram of ZYNQ chip

This development board uses Xilinx’s zynq7000 series chip, model XC7Z030-2FFG676I, 676-pin FPGA package. This chip can be divided into a PS (Processor System) part and a PL (Programmable Logic) part. On the PE7030 development board, the PS and PL sections of the XC7Z030 are both equipped with a wealth of external interfaces and devices for convenience use and functional verification. In addition, as always, the USB Cable downloader circuit is integrated on the development board. Users only need to use a USB cable to download and debug the development board.…

Read More