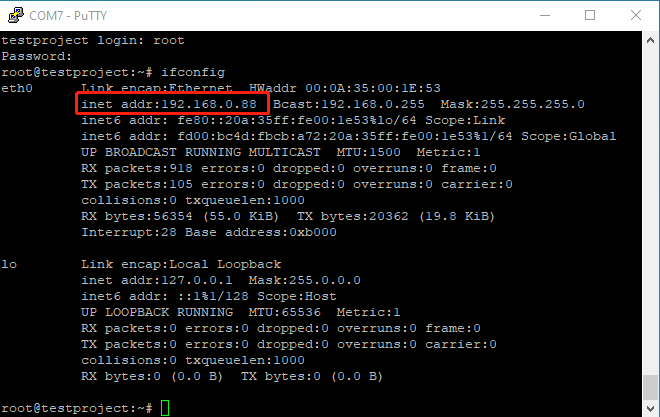

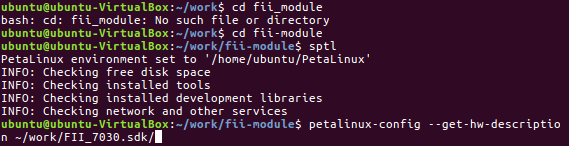

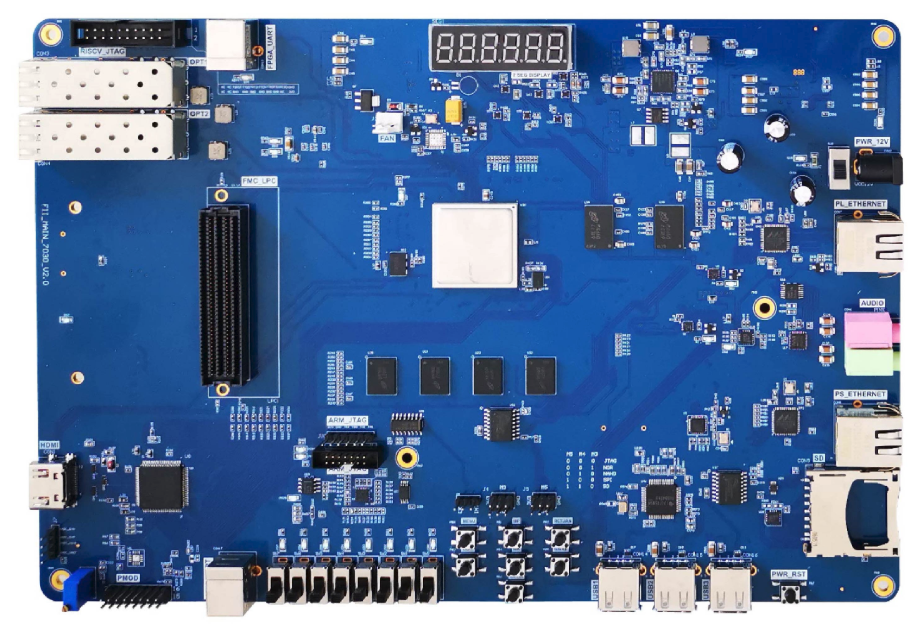

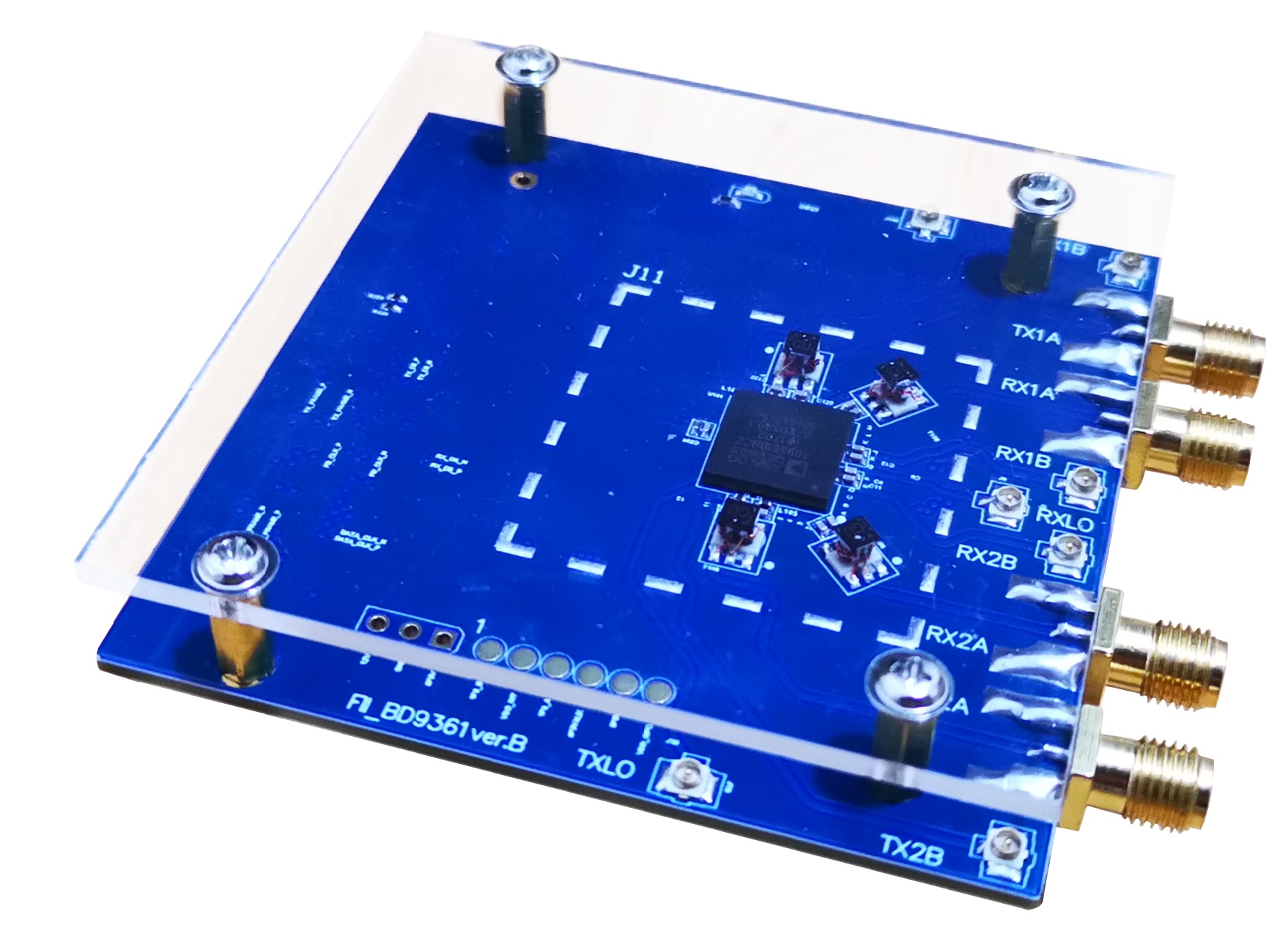

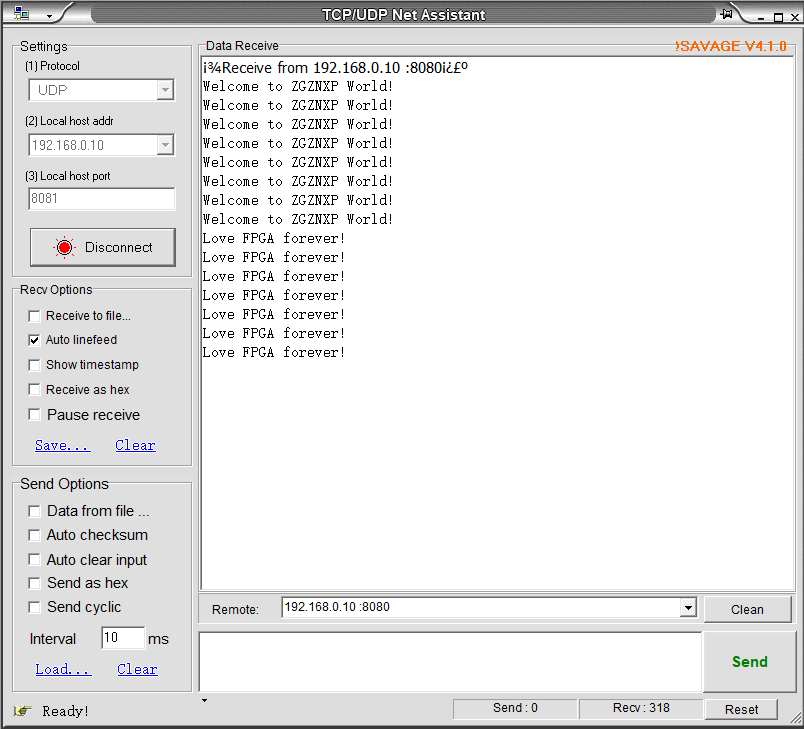

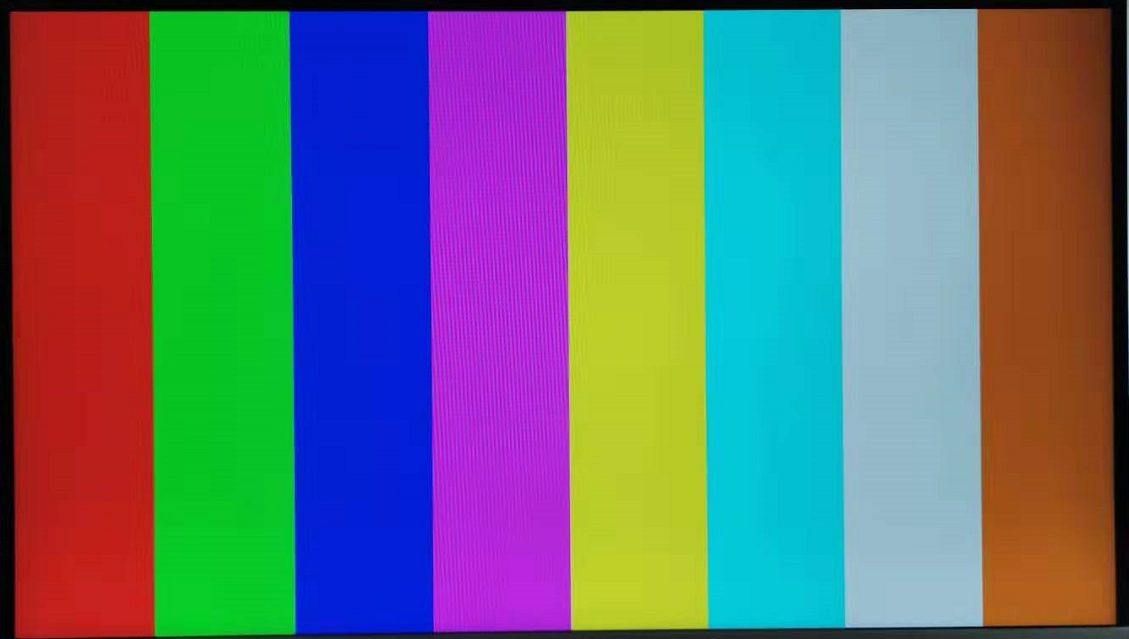

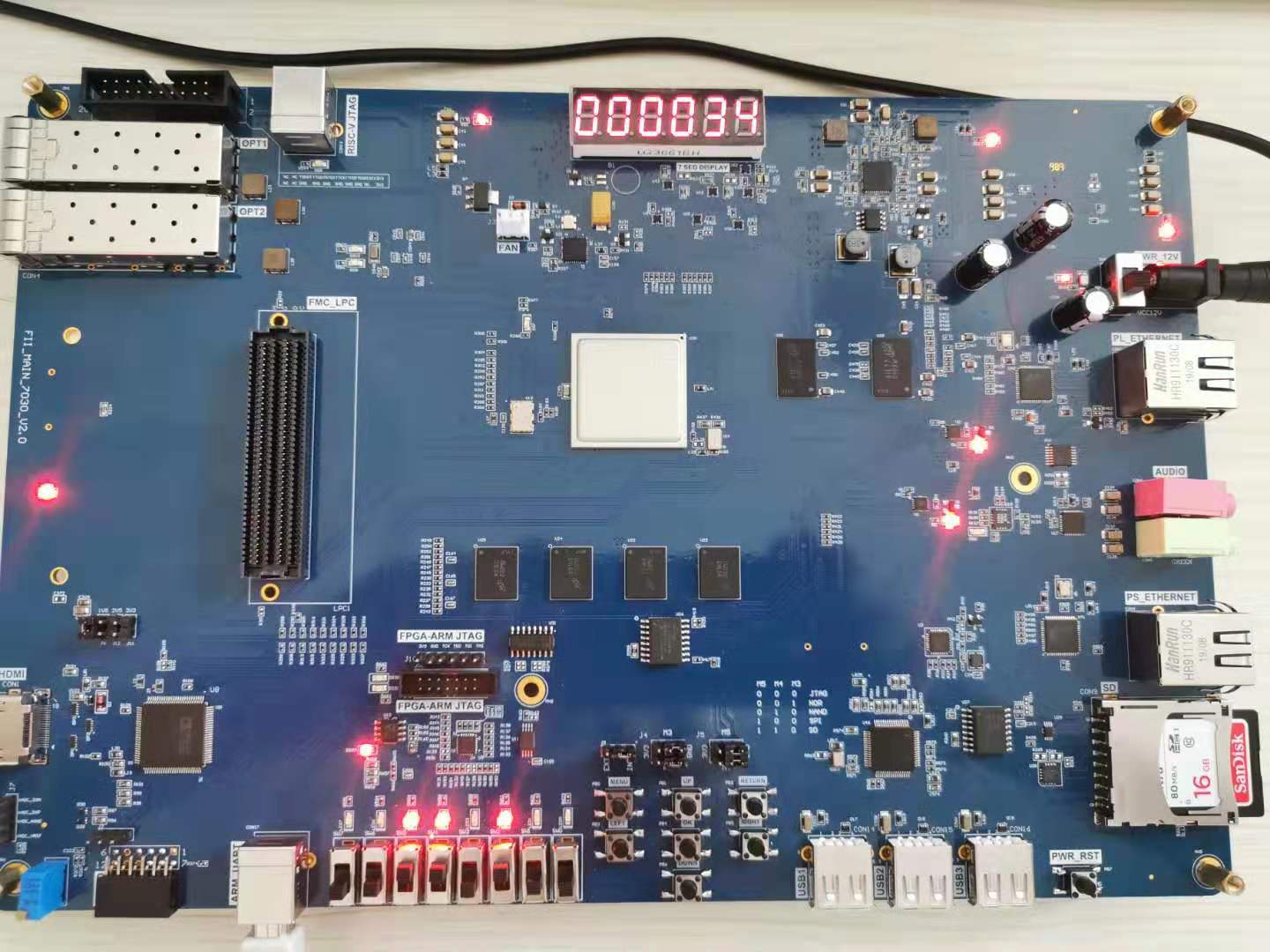

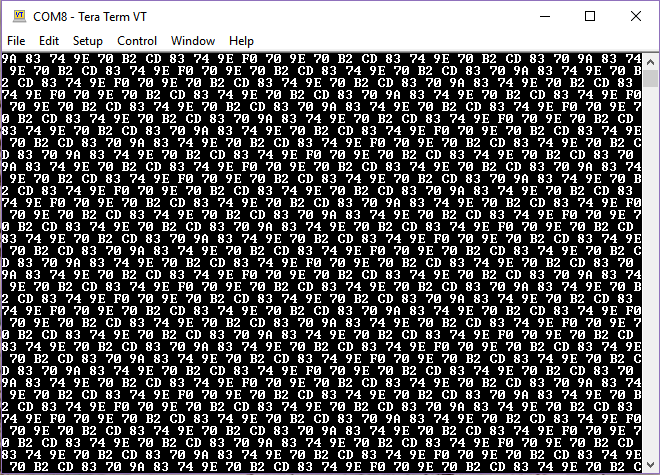

How to Use RCP, SCP, and TFTP 6 With FII-PE7030, FII-BD7100 Development Board

Table of Contents Copyright Notice 2 Section 1: Using RCP and SCP to Transfer Files 3 Section 2: Using TFTP 6 Copyright Notice: © 2020 Fraser Innovation Inc ALL RIGHTS RESERVED Without written permission of Fraser Innovation Inc, no unit or individual may extract or modify part of or all the contents of this manual. Offenders will be held liable for their legal responsibility. Thank you for purchasing the FPGA development board. Please read the manual carefully before using the product and make sure that you know how to use…

Read More