asynchronous IIC bus, and the IIC communication protocol, reading and writing EEPROM – zynq xc7z030 board – FII-PE7030 Experiment 11 – IIC Protocol Transmission

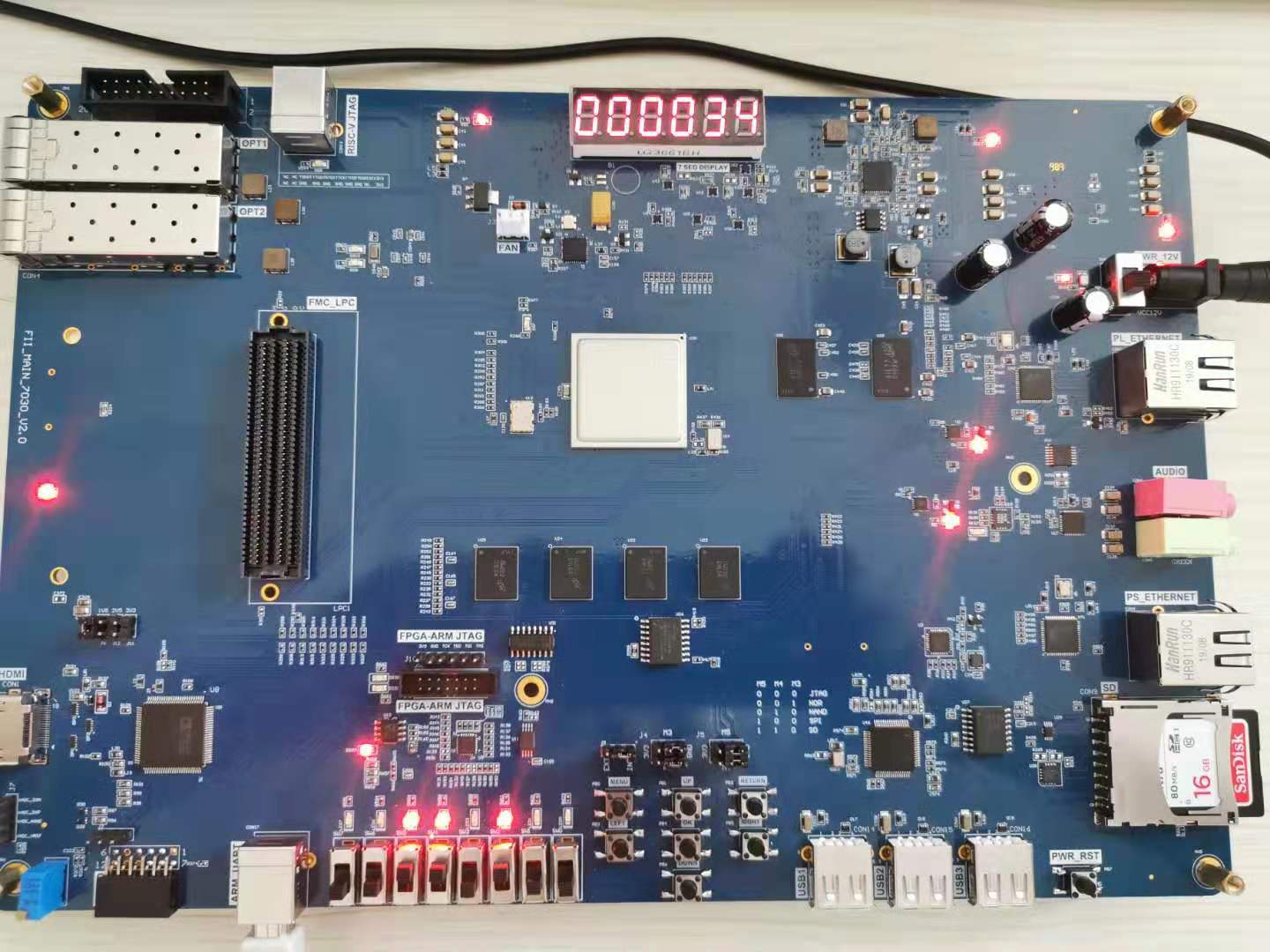

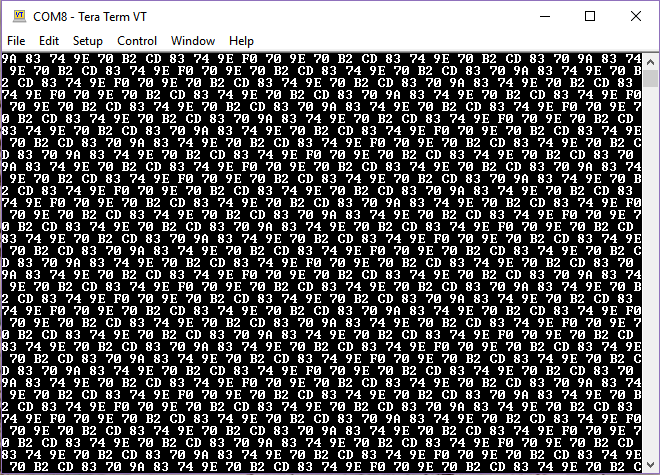

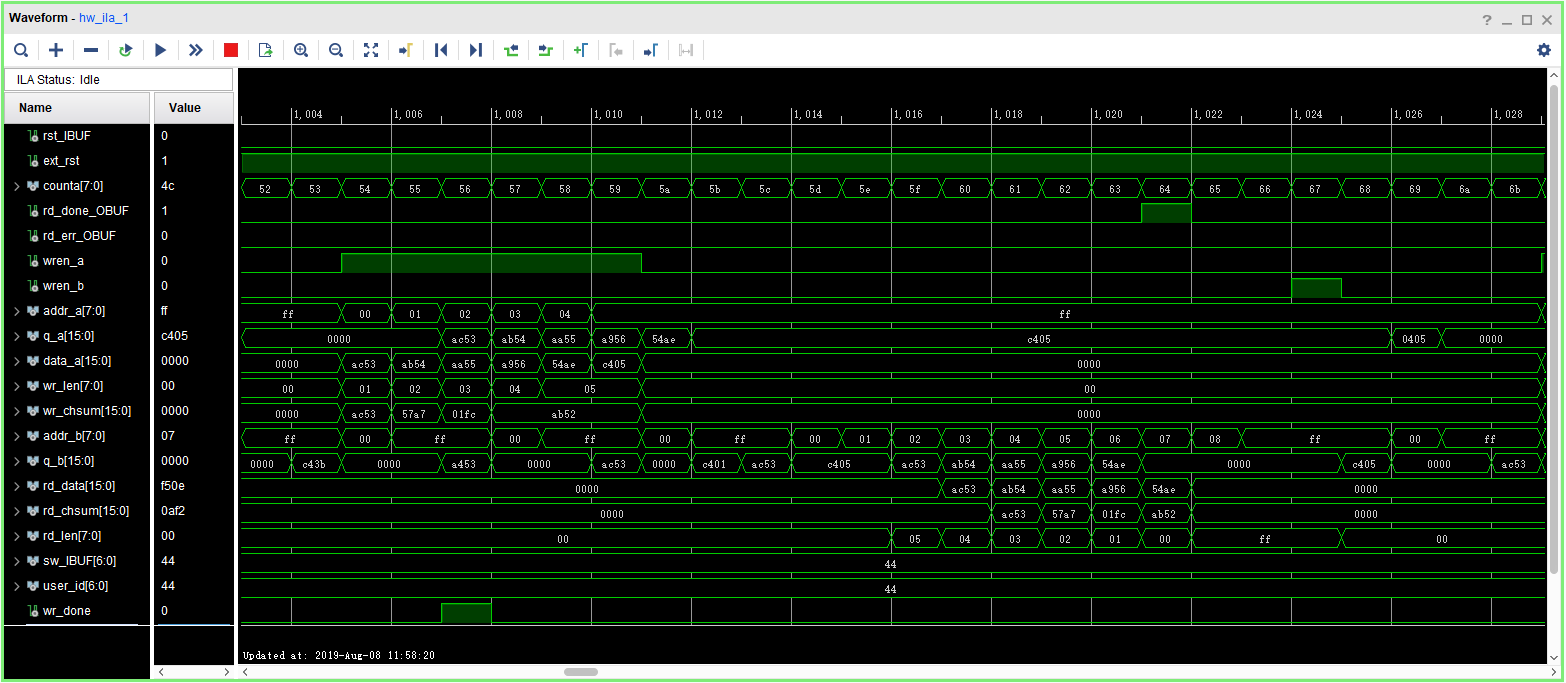

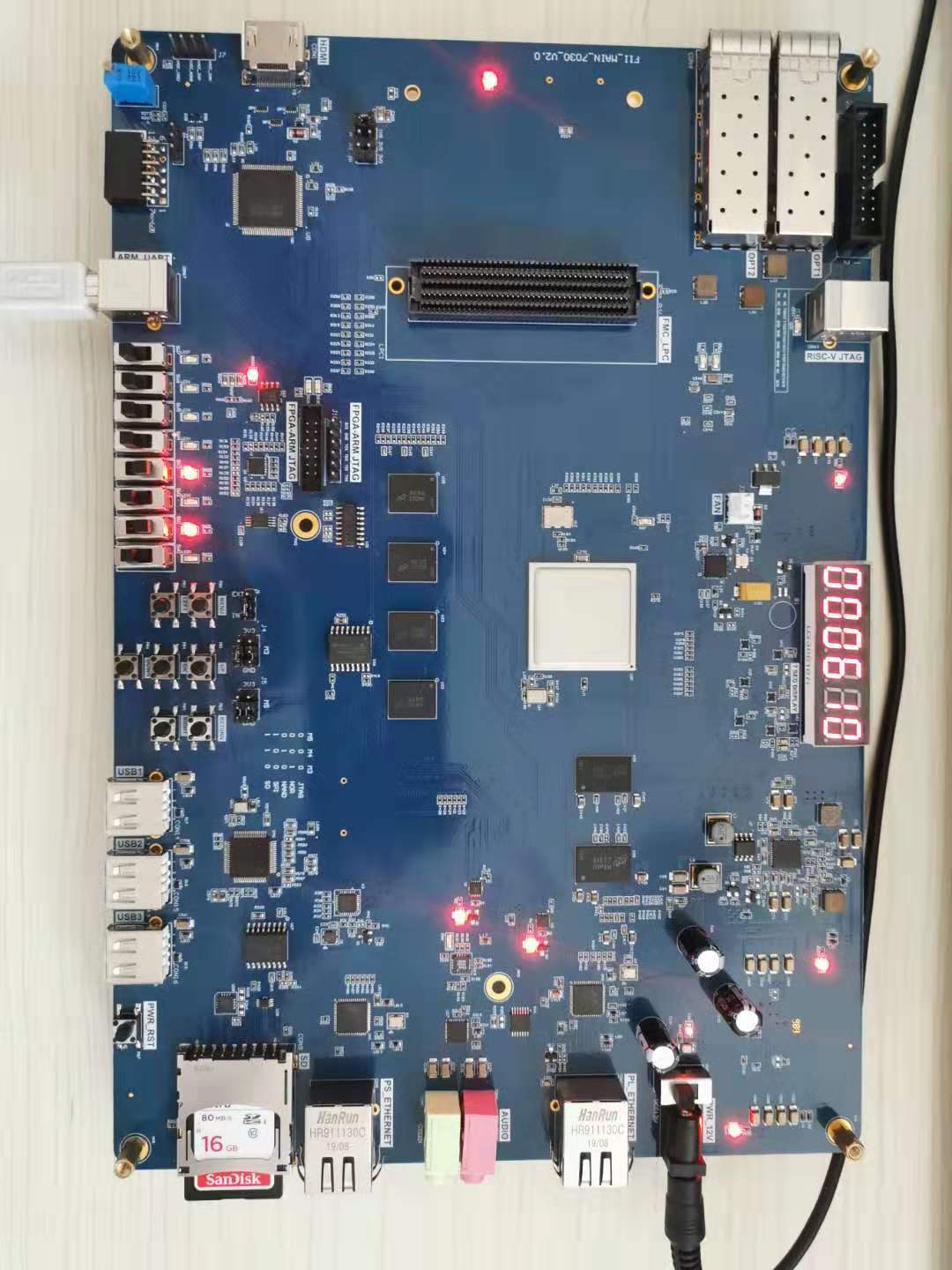

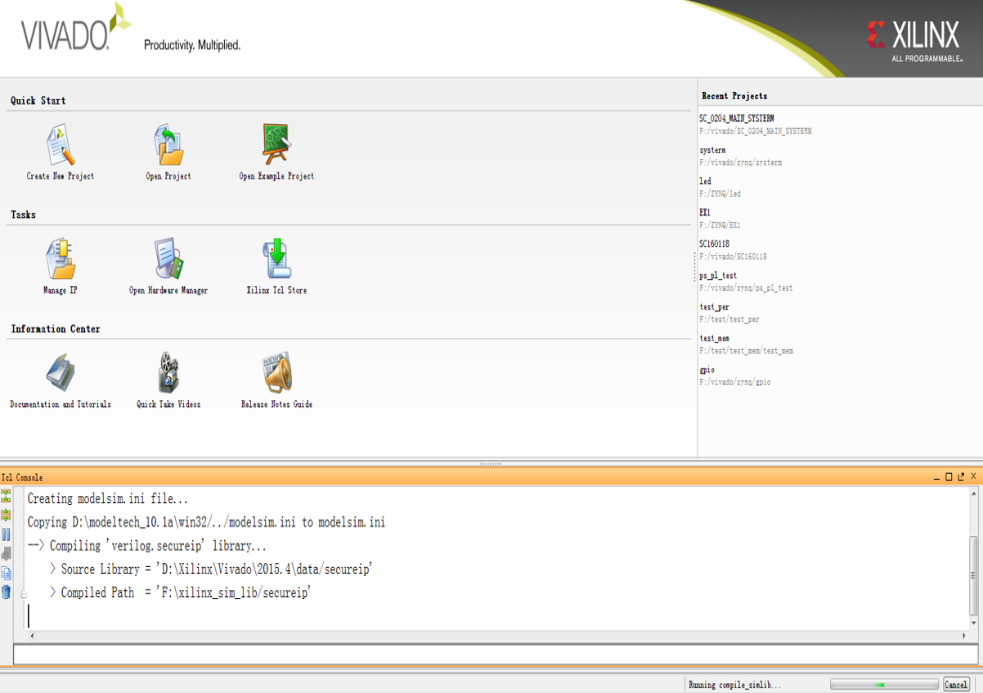

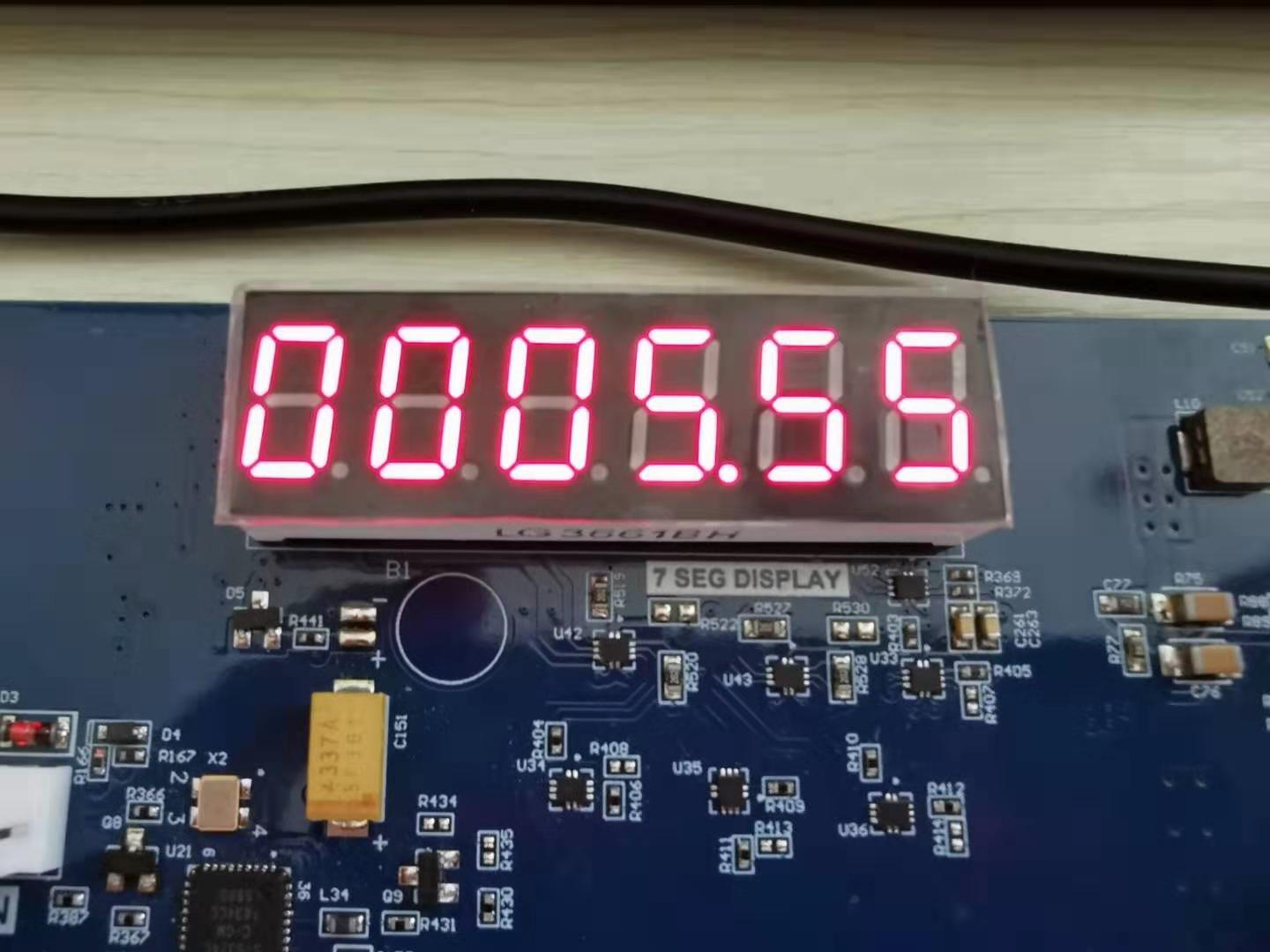

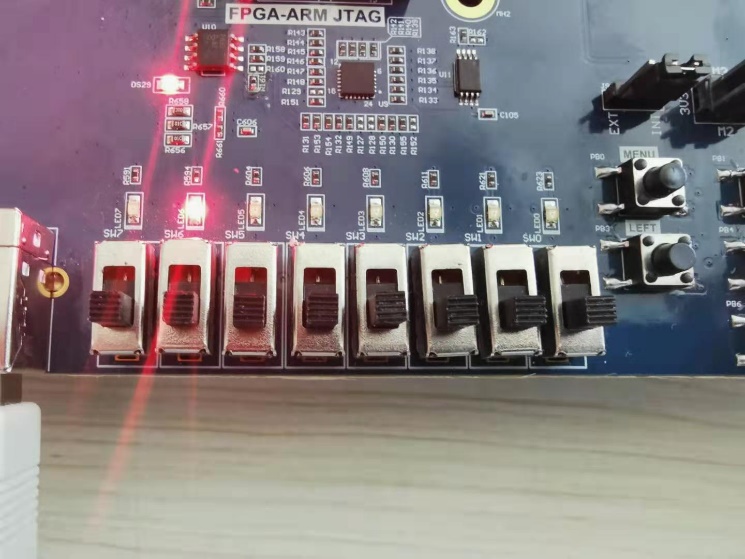

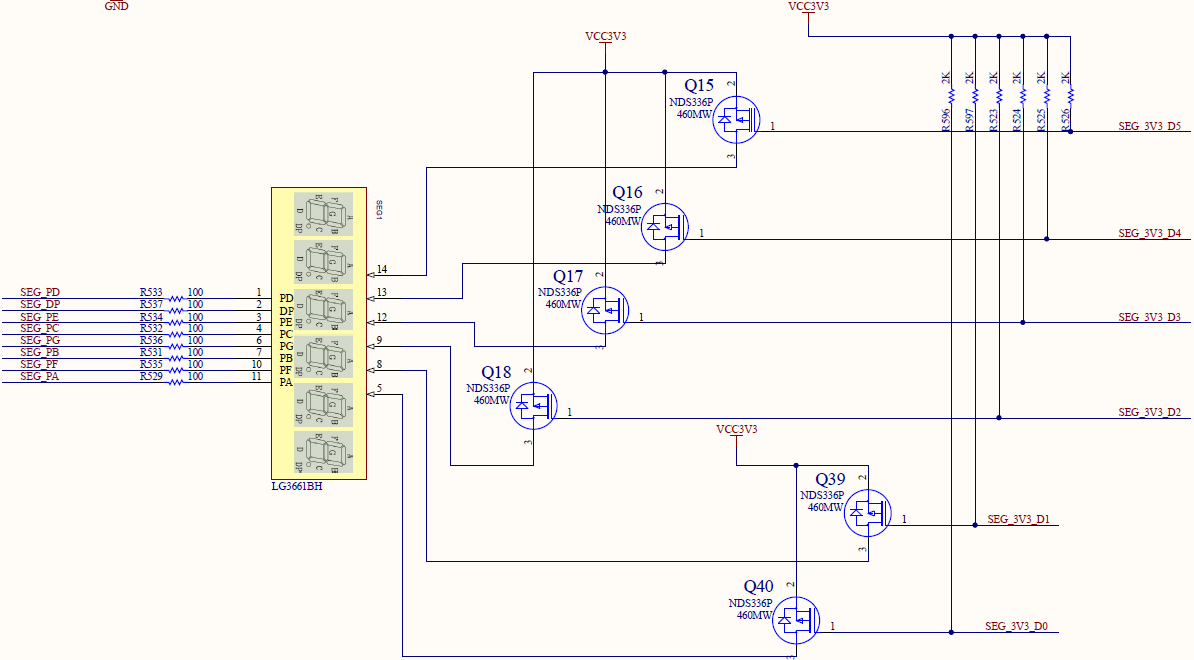

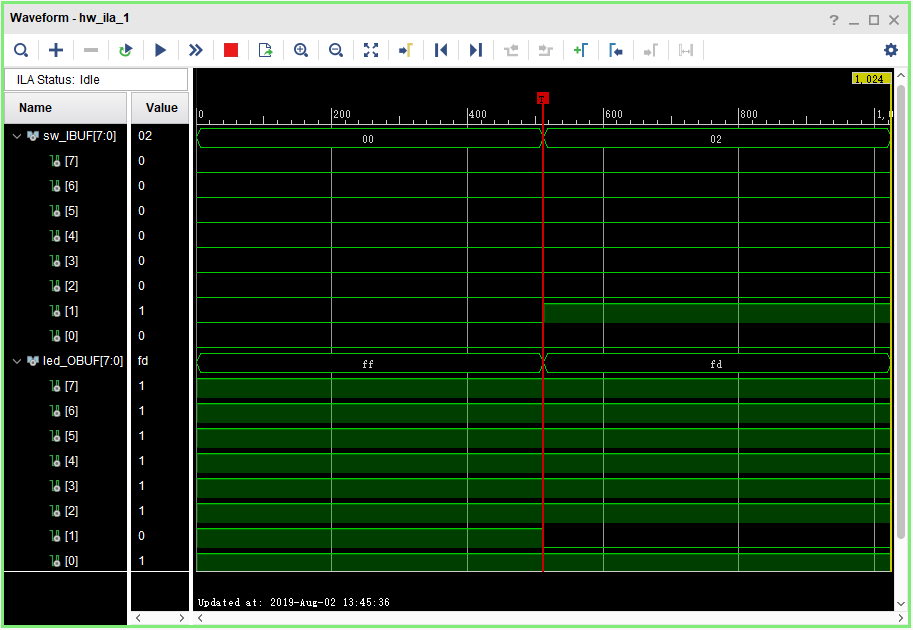

Experiment 11 IIC Protocol Transmission 11.1 Experiment Objective Learning the basic principles of asynchronous IIC bus, and the IIC communication protocol Master the method of reading and writing EEPROM Joint debugging using logic analyzer 11.2 Experiment Implement Correctly write a number to any address in the EEPROM (this experiment writes to the register of 8’h03 address) through the FPGA (here changes the written 8-bit data value by (SW7~SW0)). After writing in successfully, read the data as well. The read data is displayed directly on the segment display. Download the program…

Read More