Learn HDMI principle, Introduction to HDMI and ADV7511 Chip, HDMI Display, FII-PRA040 Altera Risc-V tutorial Experiment 13

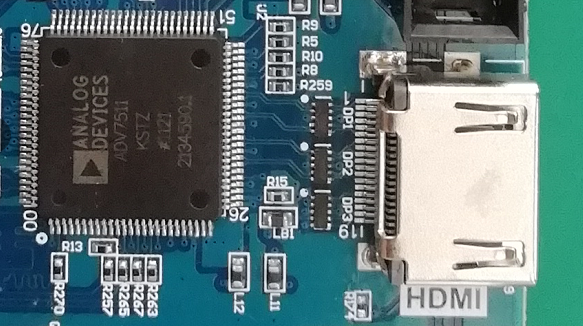

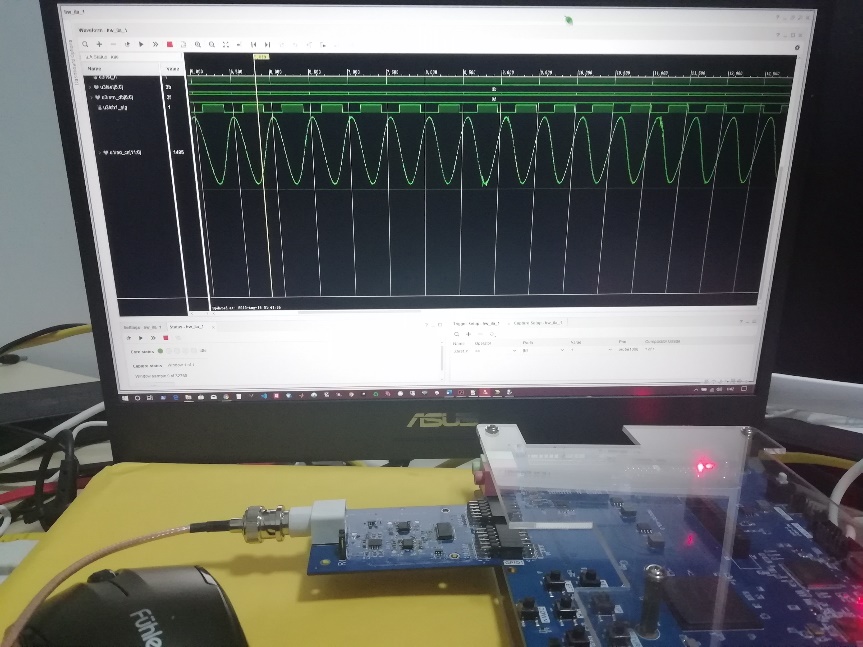

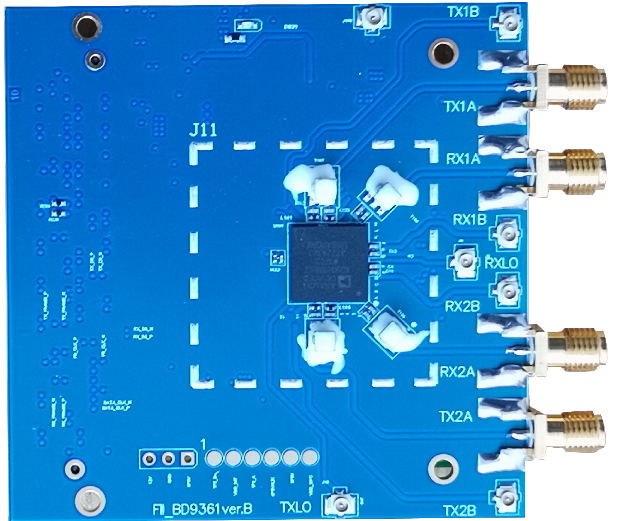

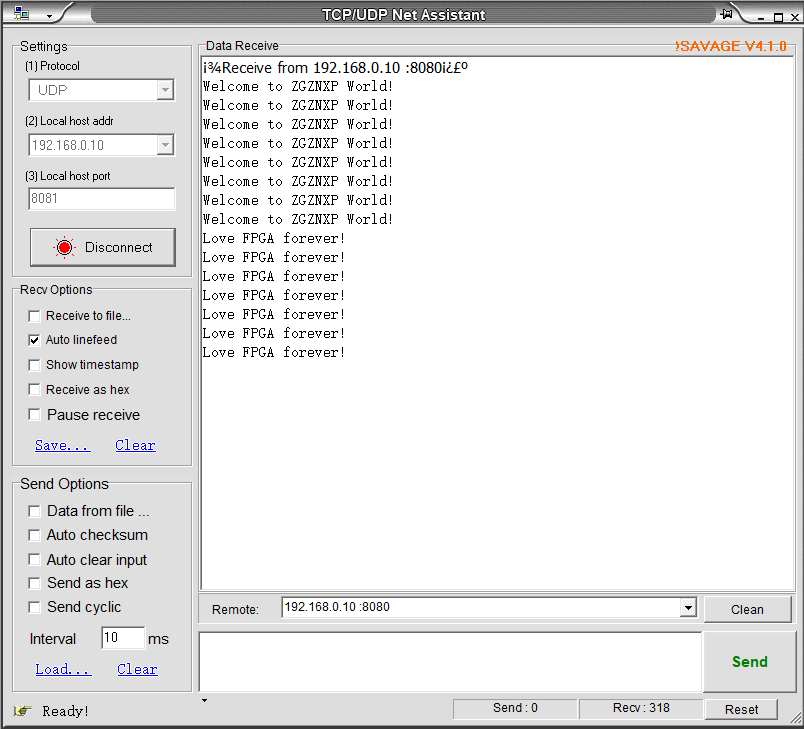

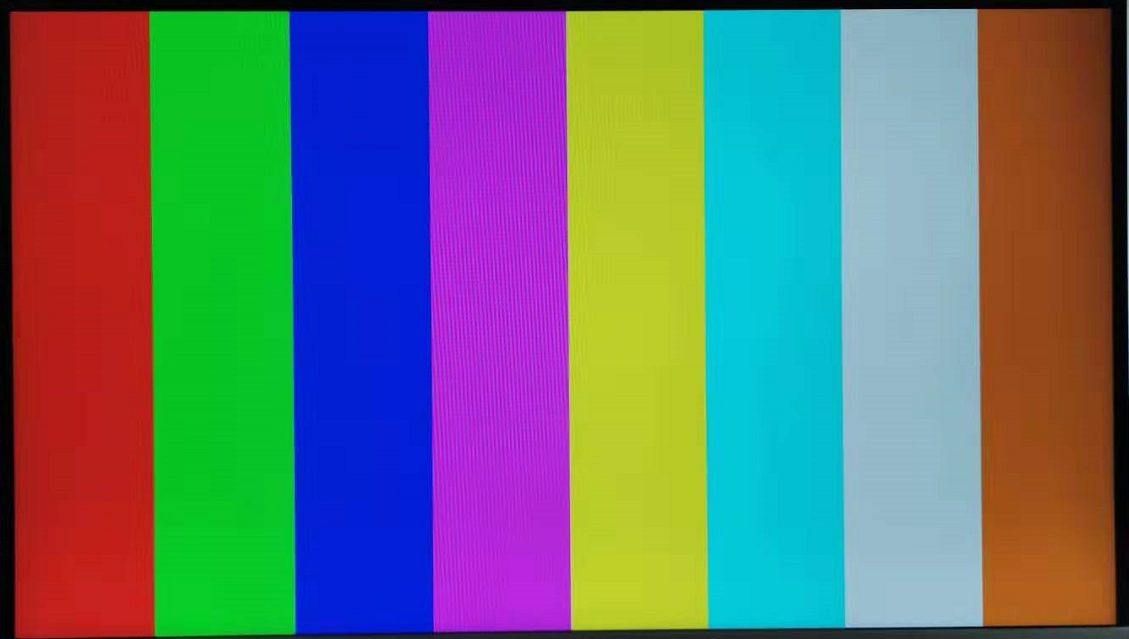

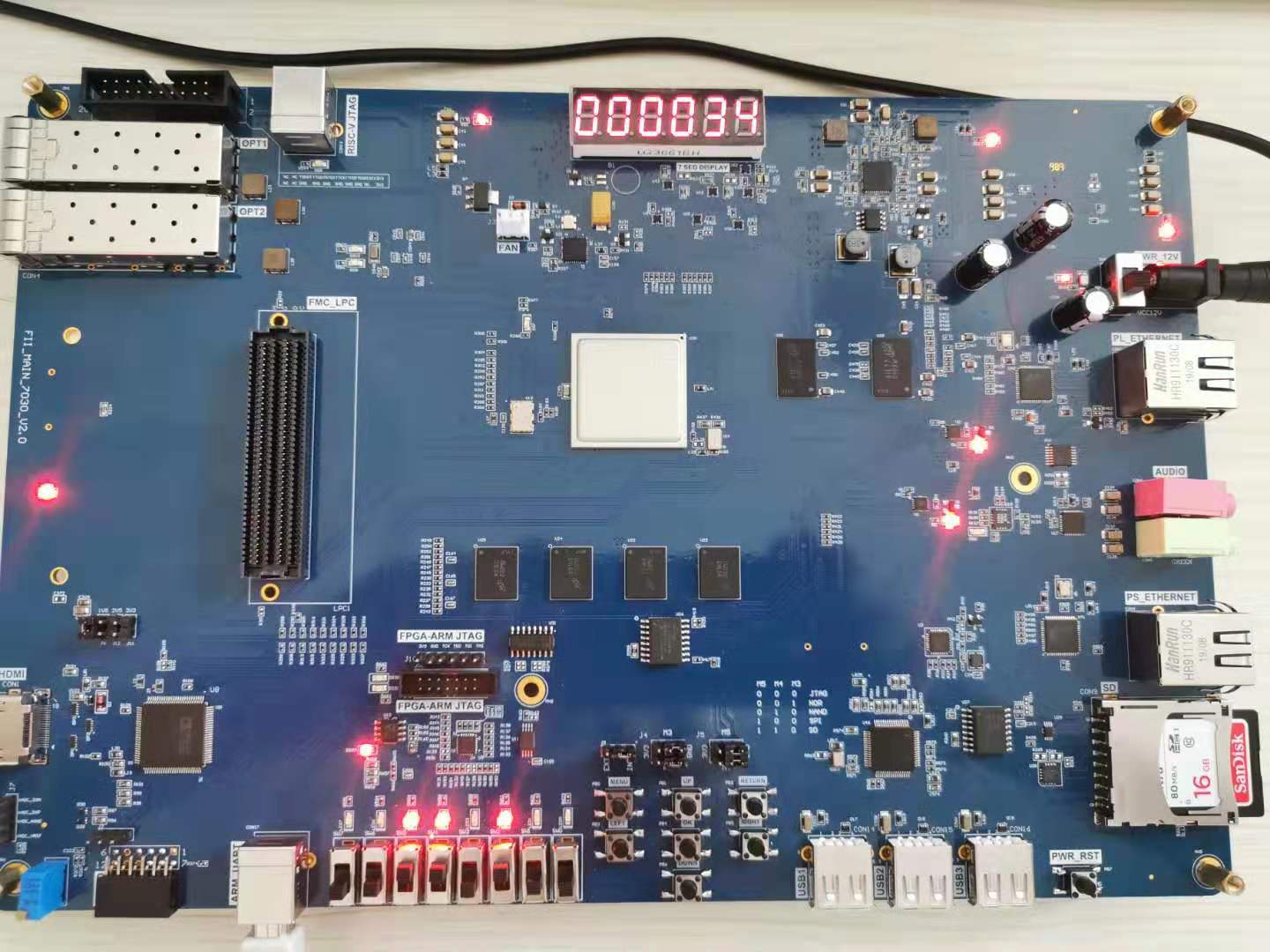

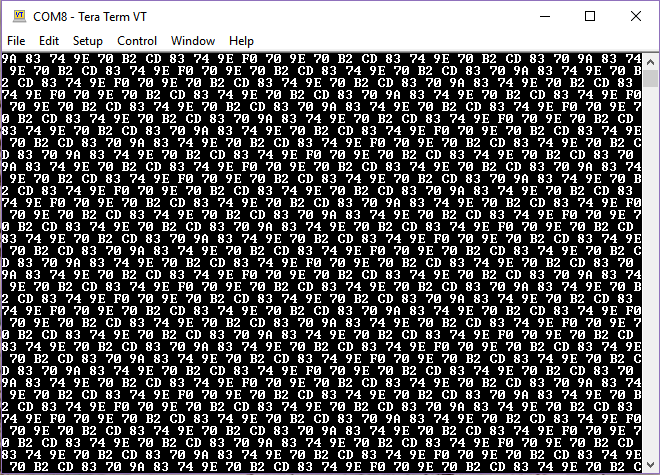

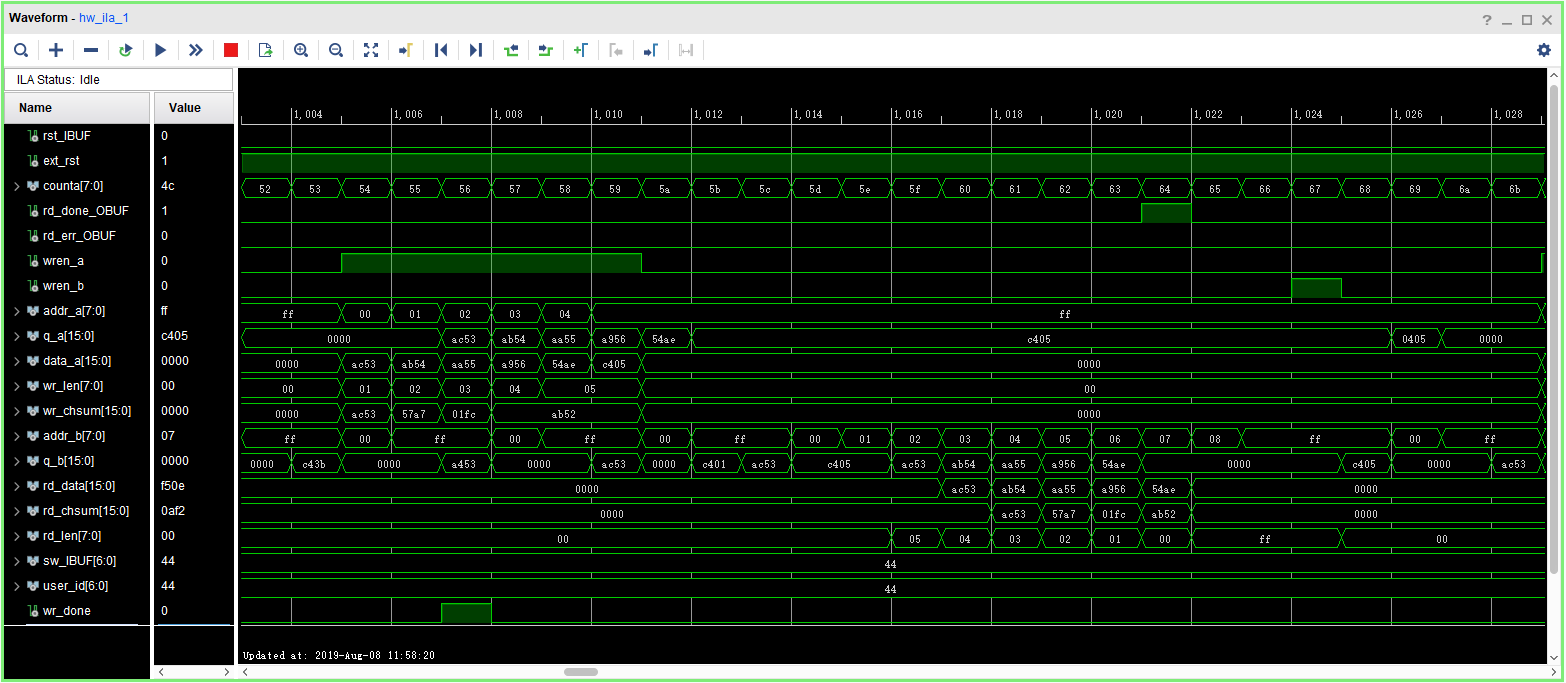

Experiment 13 HDMI Display 13.1 Experiment Objective Review IIC protocol Review EEPROM read and write Learn HDMI principle 13.2 Experiment Implement Display different image content on the screen through the HDMI. 13.3 Experiment 13.3.1 Introduction to HDMI and ADV7511 Chip Image display processing has always been the focus of FPGA research. At present, the image display mode is also developing. The image display interface is also gradually transitioning from the old VGA interface to the new DVI or HDMI interface. HDMI (High Definition Multimedia Interface) is a digital video/audio interface…

Read More