Verilog HDL program to achieve frequency division, Write Verilog HDL program to implement LED shifting – Risc-V FPGA Board Xilinx – Development Board Experiment 1 – LED Shifting – FII-PRX100

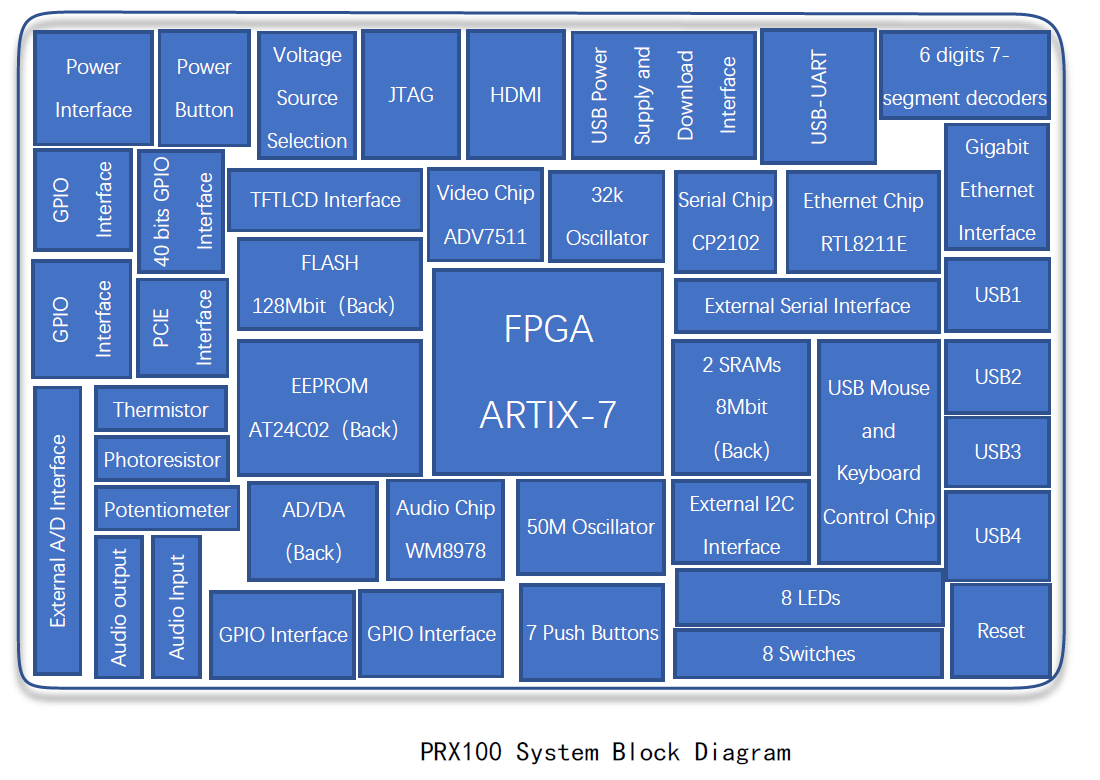

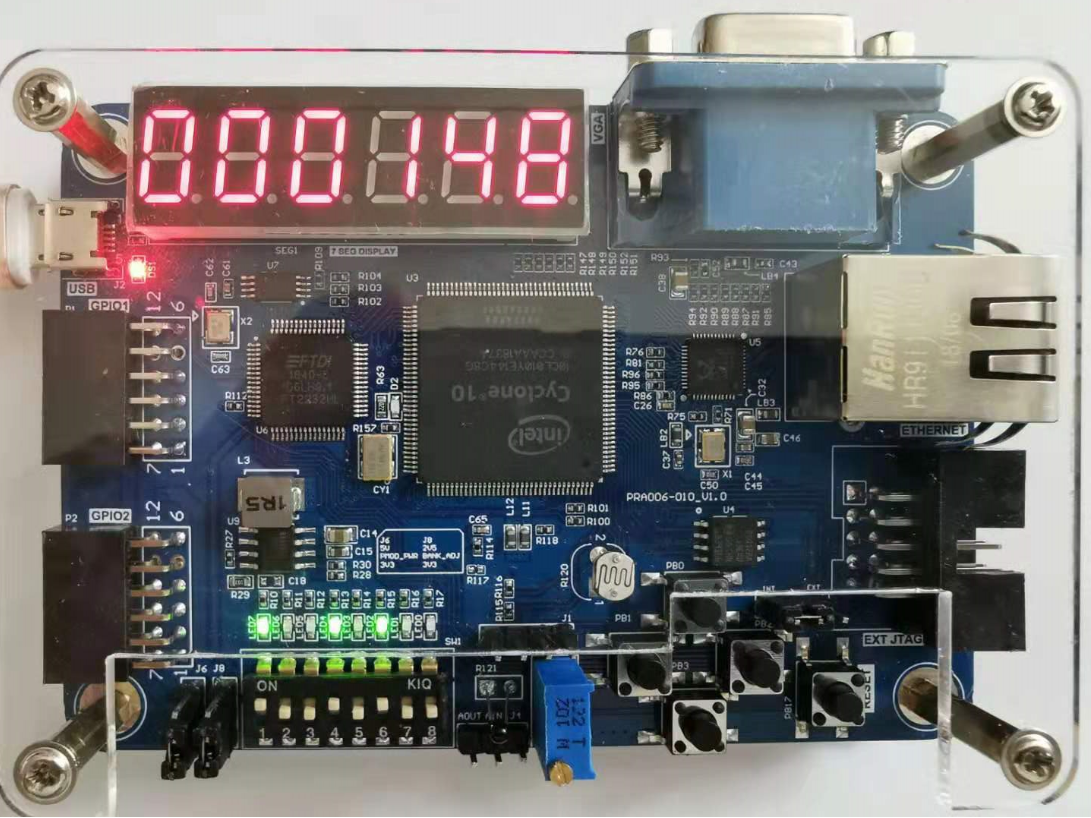

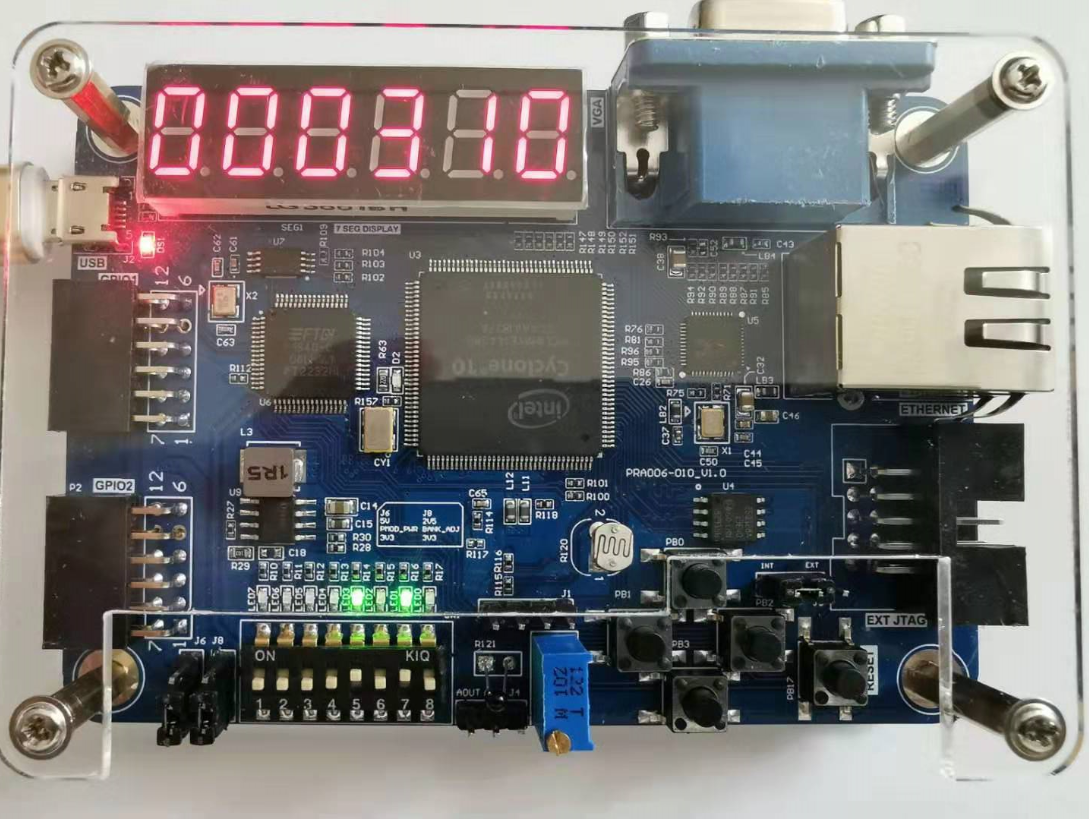

Experiment 1 LED Shifting 1. Experiment Object Practice how to use the development system software Vivado to establish a new project, call the system resource PLL to establish the clock. Write Verilog HDL program to achieve frequency division Write Verilog HDL program to implement LED shifting Combine hardware resources for FPGA pin configuration Compile Download the program to the develop board Observe the experimental result and debug the project 2. Create A New Project Under Vivado Start Vivado in the start Menu. See Fig 1. 1 Fig 1. 1 Start…

Read More