Building new FPGA Projects in Quartus, Device Selection, PLL setup, PLL Frequency Setting, Verilog’s Tree Hierarchy Design, and the Use of SignalTap II – Block/SCH Experiment – FPGA Beginner Study Board PRA006, PRA010 Experiment 4

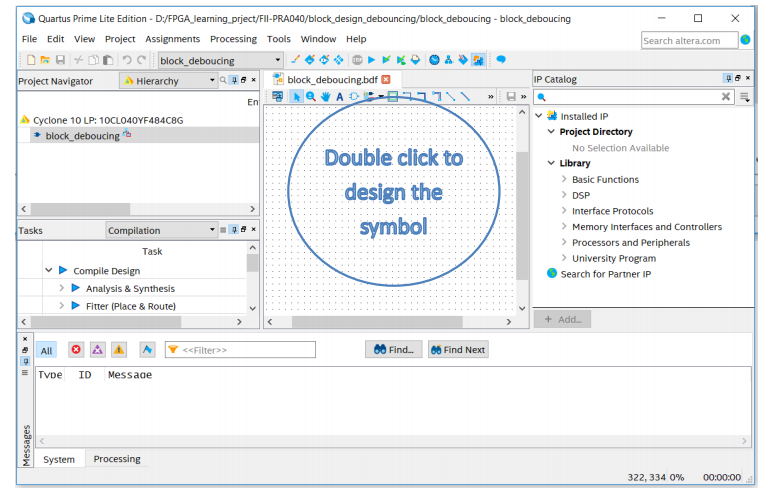

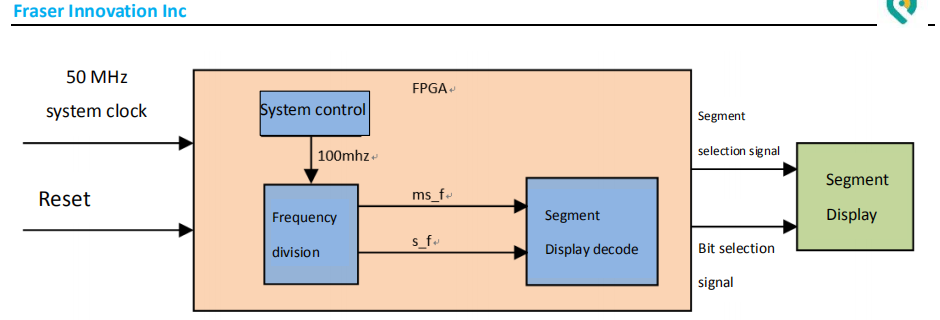

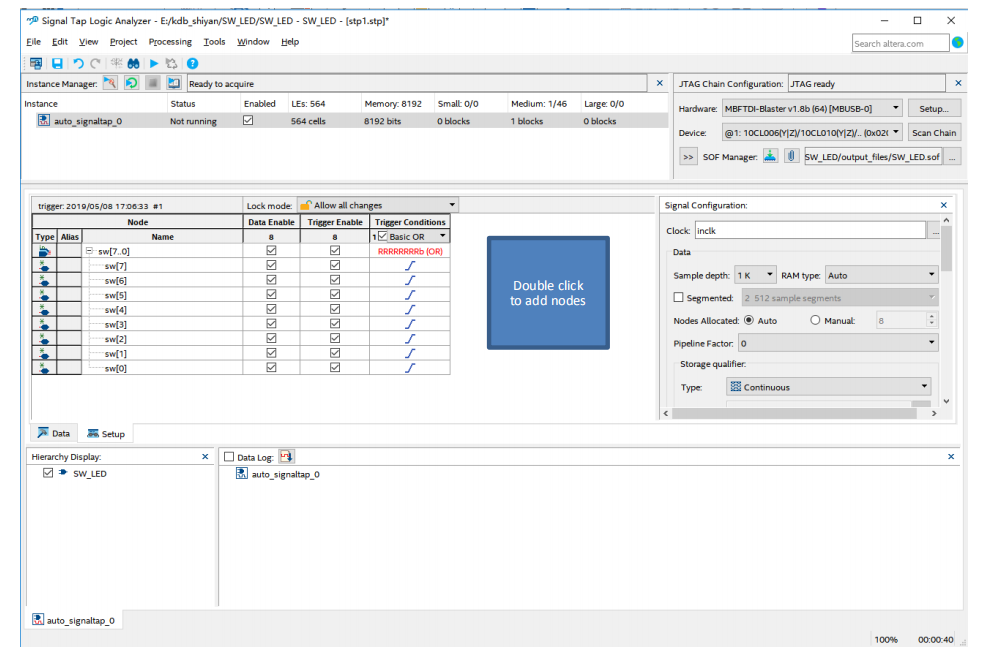

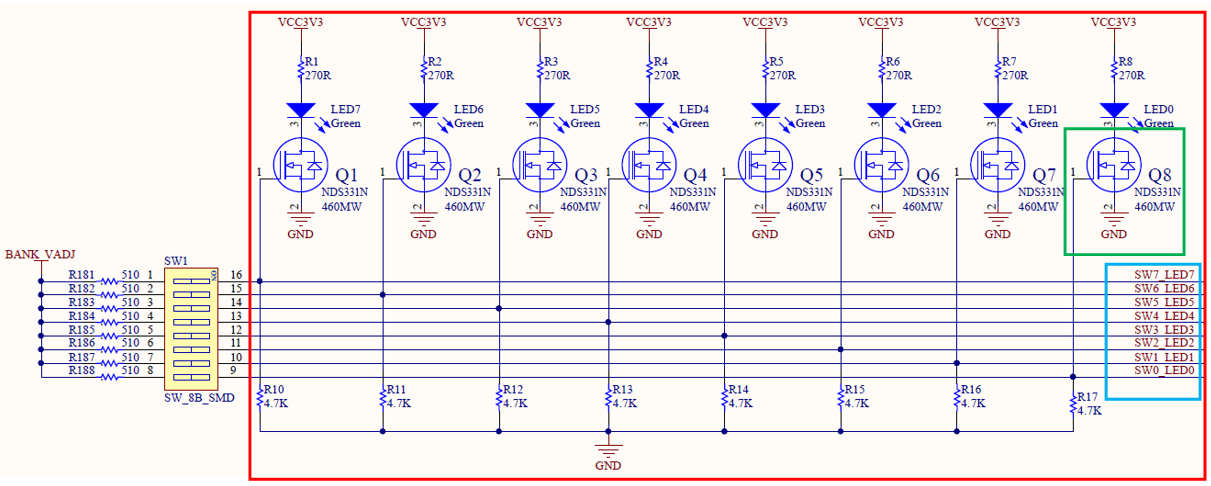

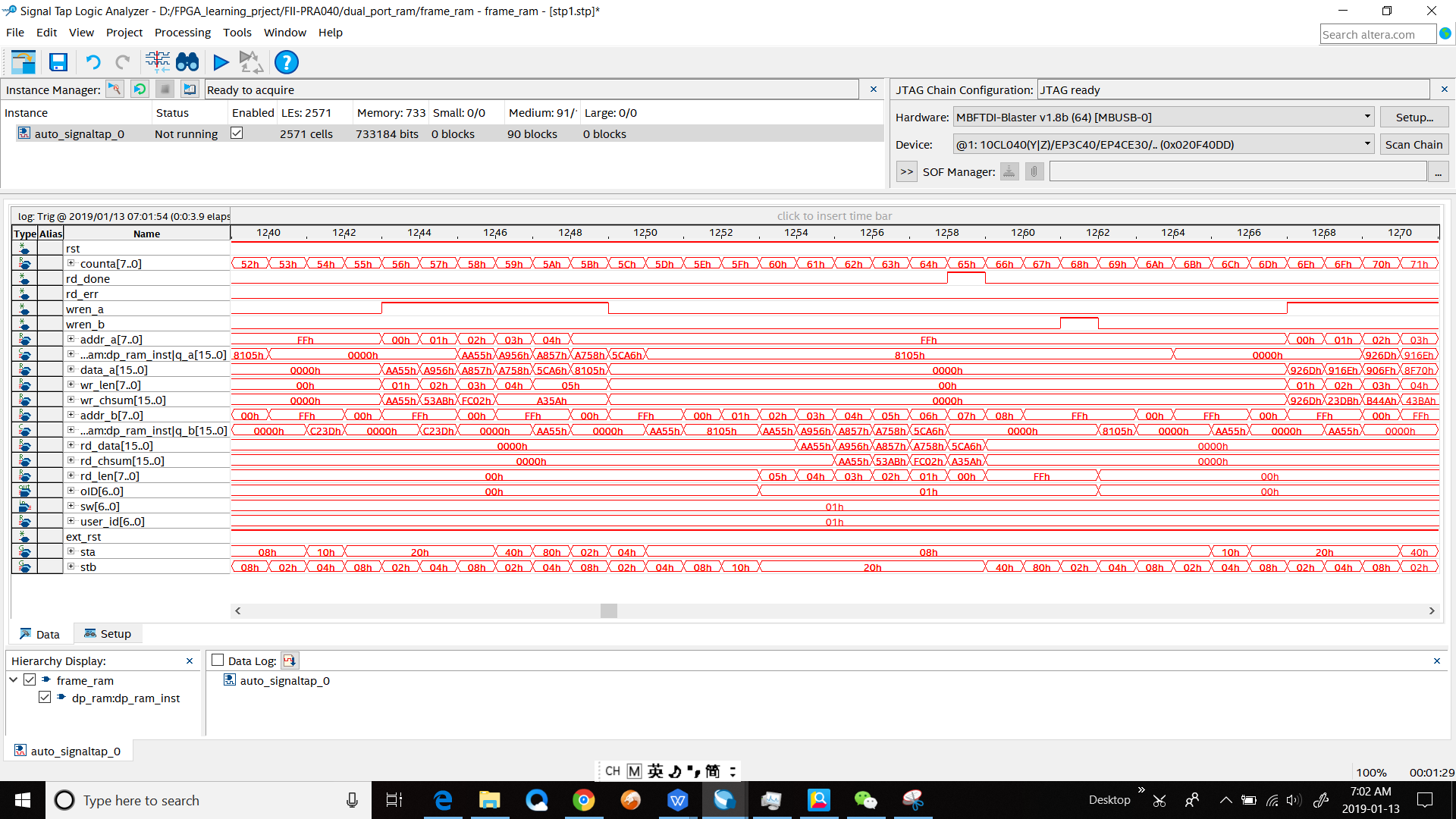

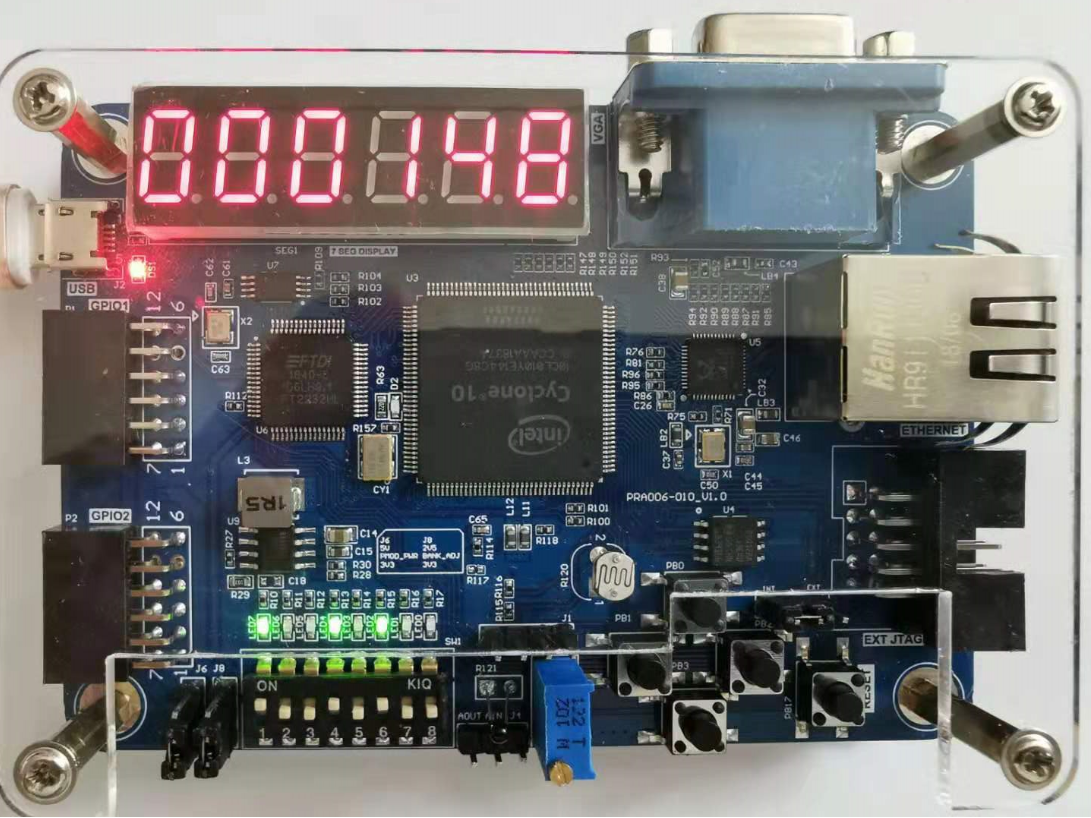

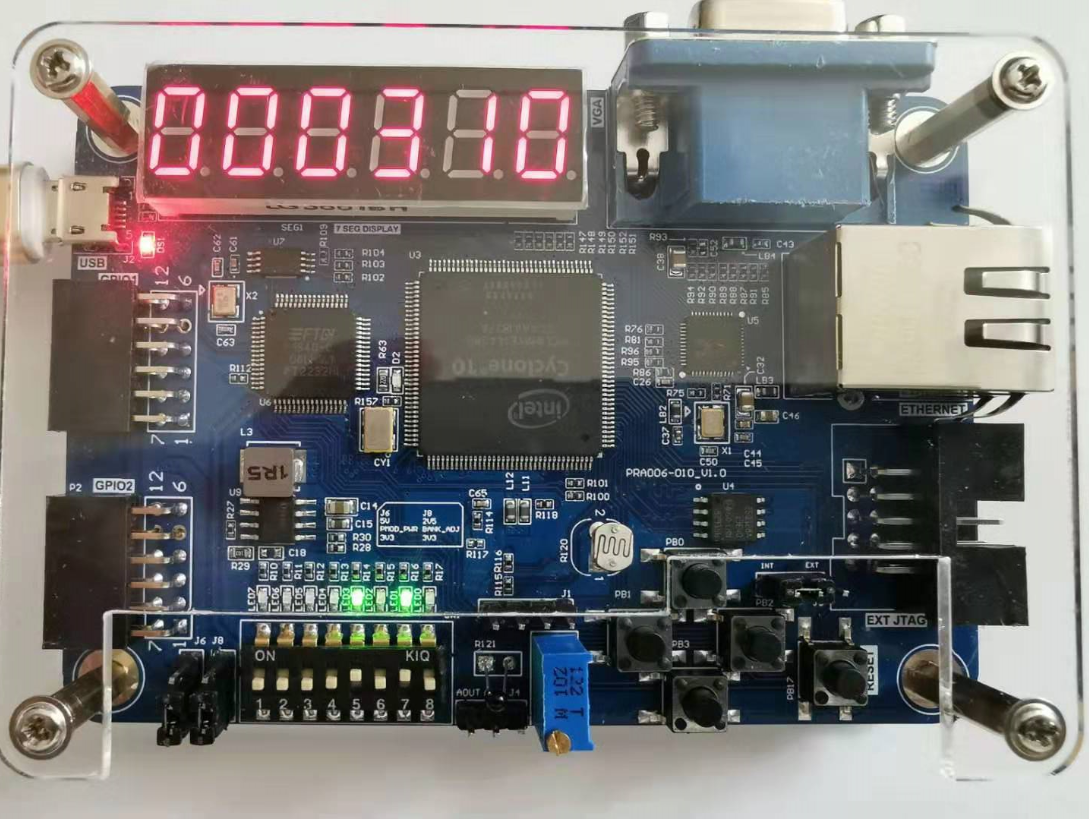

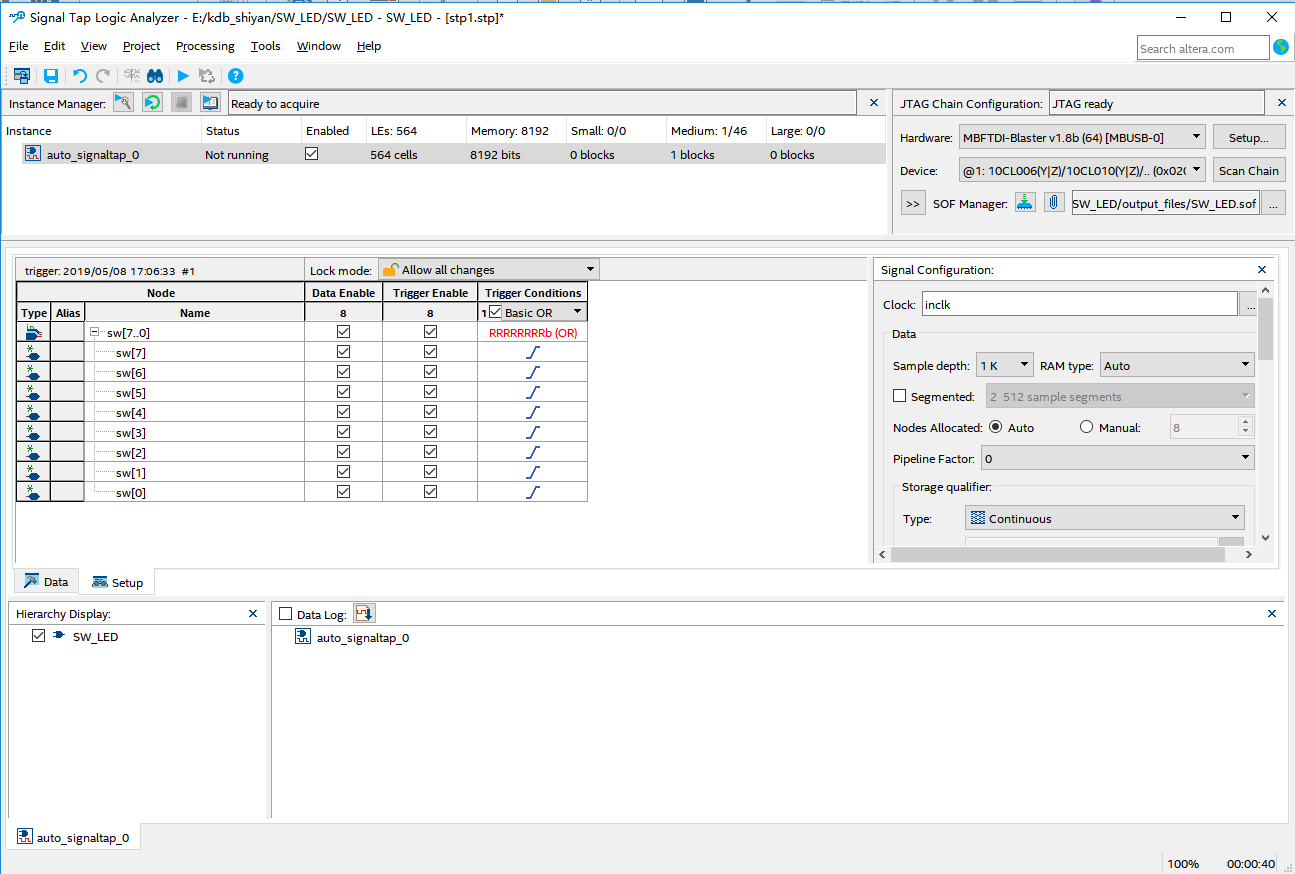

Experiment 4 Block/SCH Experiment 4.1 Experiment Objective Review building new FPGA projects in Quartus, device selection, PLL setup, PLL frequency setting, Verilog’s tree hierarchy design, and the use of SignalTap II Master the design method of graphics from top to bottom Combined with the BCD_counter project to achieve the display of the digital clock Observe the experimental results 4.2 Experiment Implement Use schematics design to build the project 4.3 Experiment This experiment is mainly to master another design method. The other design contents are basically the same as the experiment…

Read More