Use ModelSim Simulation to Design Output, Use of Multipliers and ModelSim Simulation – FPGA Beginner Study Board PRA006, PRA010 Experiment 6

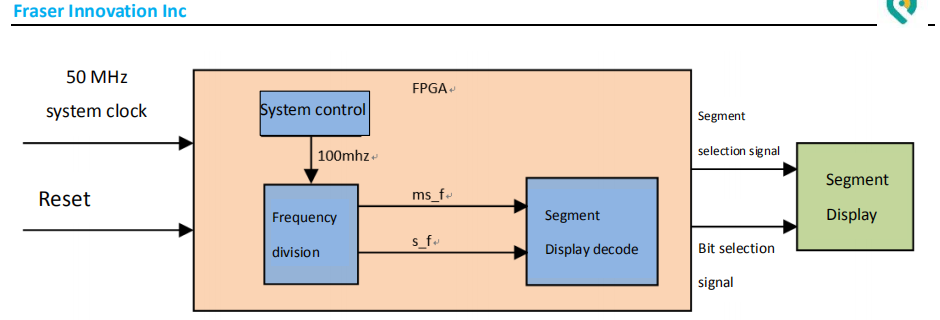

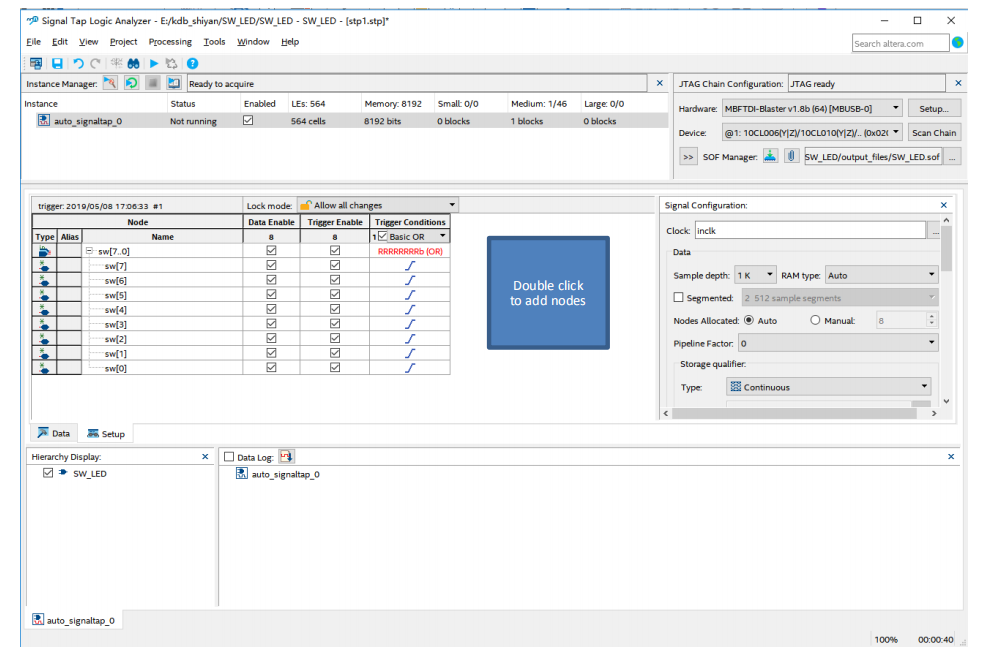

Experiment 6 Use of Multipliers and ModelSim Simulation 6.1 Experiment Objective Learn to use multiplier Use ModelSim simulation to design output 6.2 Experiment Implement 8×8 multiplier, the first input value is an 8-bit switch, and the second input value is the output of an 8-bit counter. Observe the output in ModelSim Oberseve the calculation results with a four-digit segment display 6.3 Experiment Since the simulation tools and the new IP core are used here, there is no introduction or design part of hardware. 6.3.1 Introduction of Program ModelSim is an…

Read More