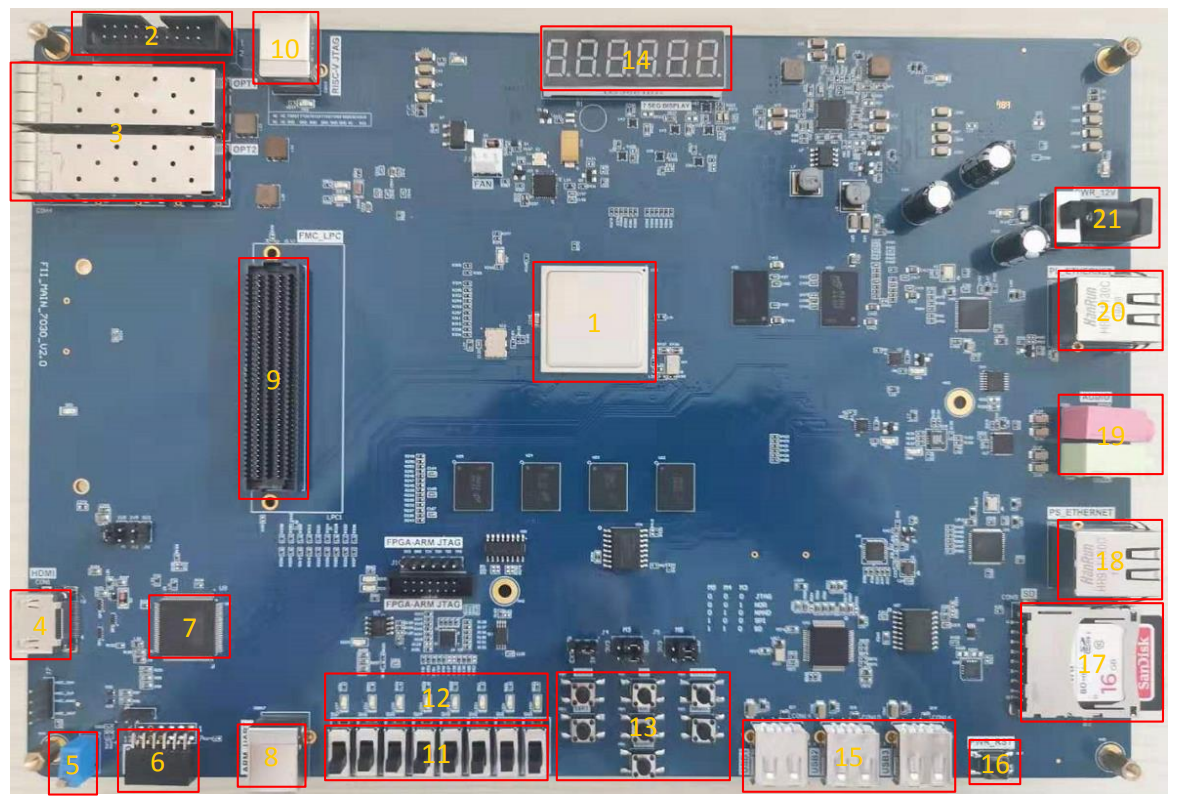

zynq xc7z030 board – FII-PE7030 Experiment 6 – Use of Multipliers and ISIM

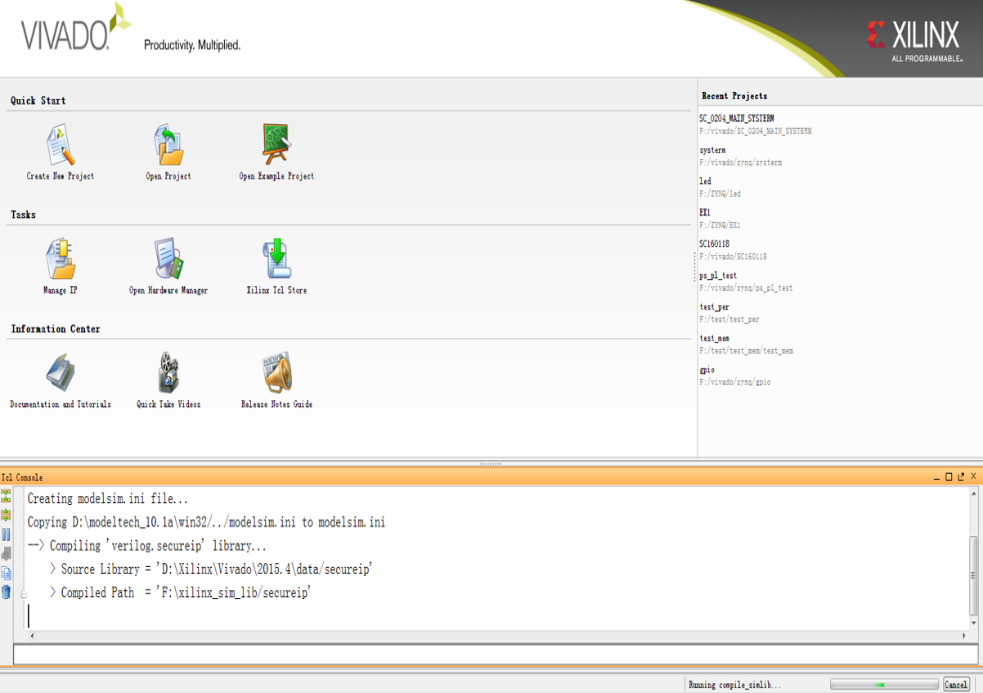

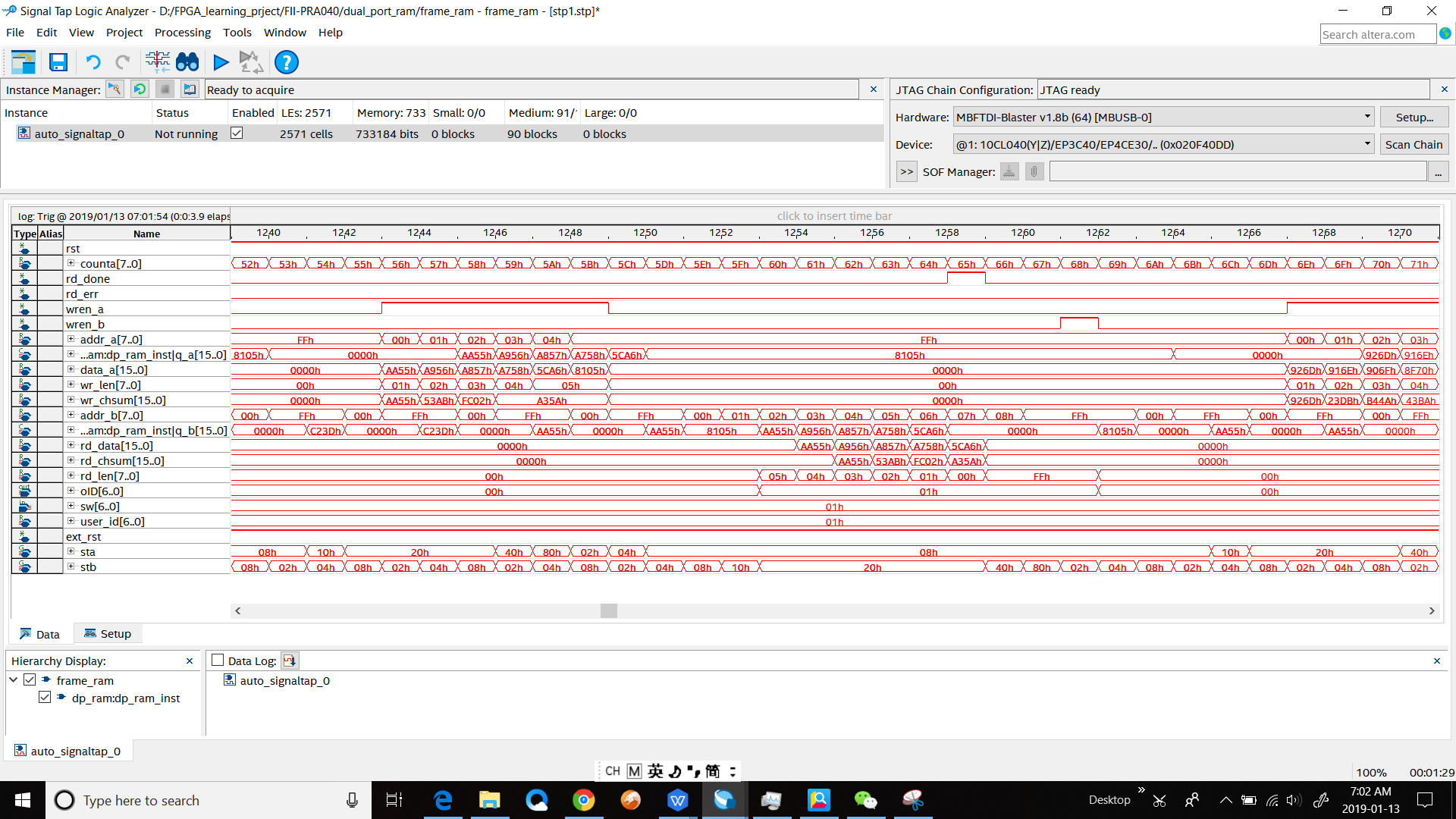

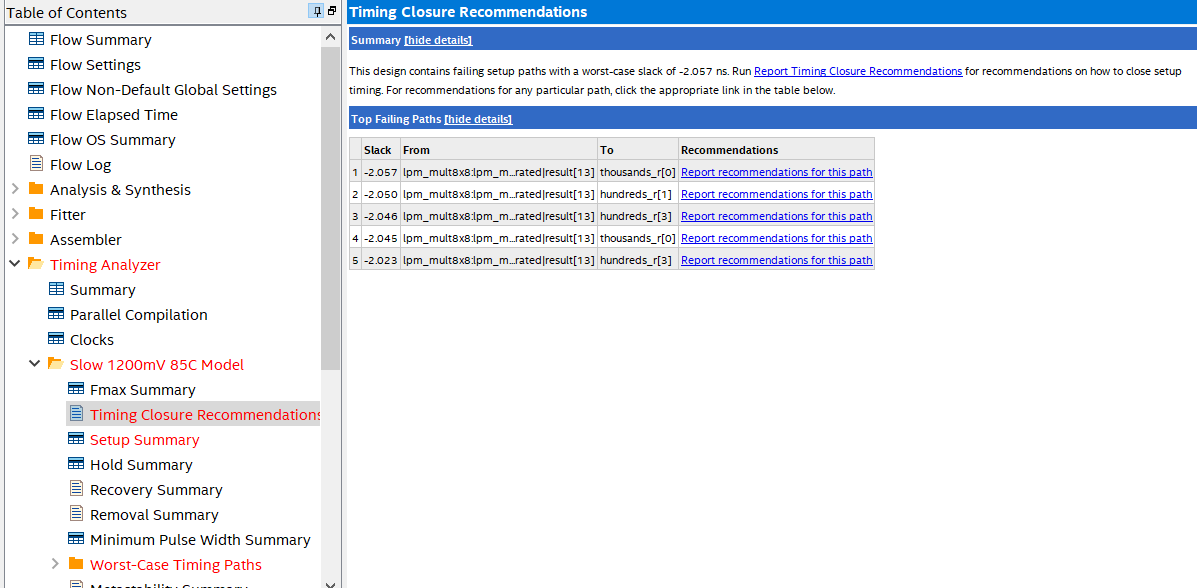

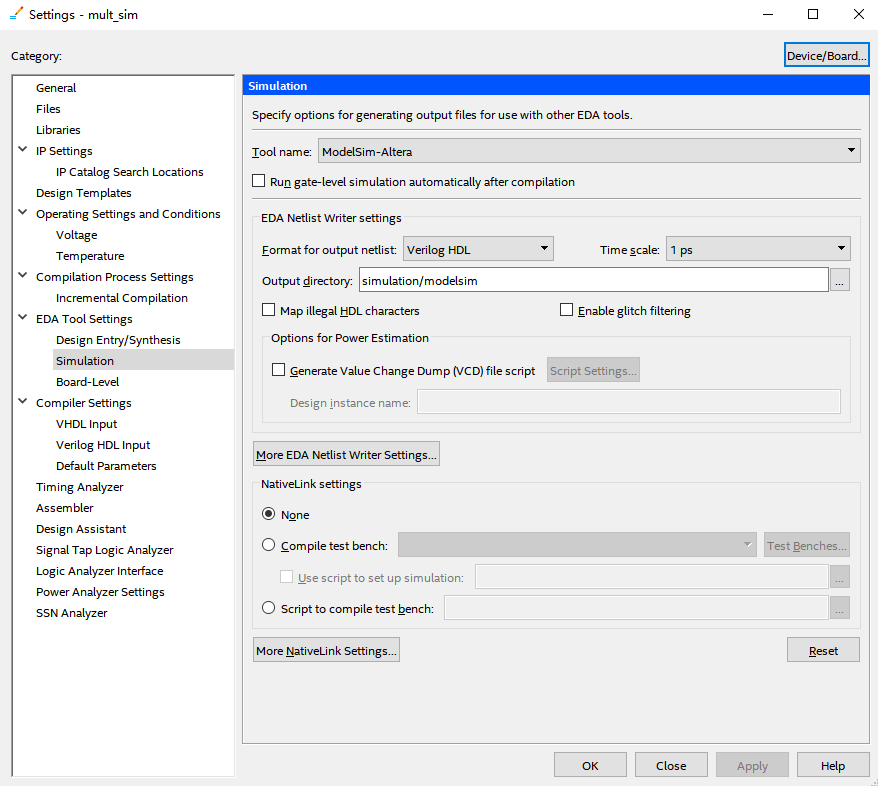

Experiment 6 Use of Multipliers and ISIM 6.1 Experiment Objective Learn to use multiplier Use ISIM to simulate design output 6.2 Experiment Implement 8×8 multiplier, the first input value is an 8-bit switch, and the second input value is the output of an 8-bit counter. Observe the output in ISIM 6.3 Experiment 6.3.1 Program Design The first step: the establishment of the main program framework module mult_sim( input inclk_p, input inclk_n, input [7:0] sw, output [15:0] mult_res, output reg [7:0] count ); endmodule The second step: call multiplier IP core…

Read More