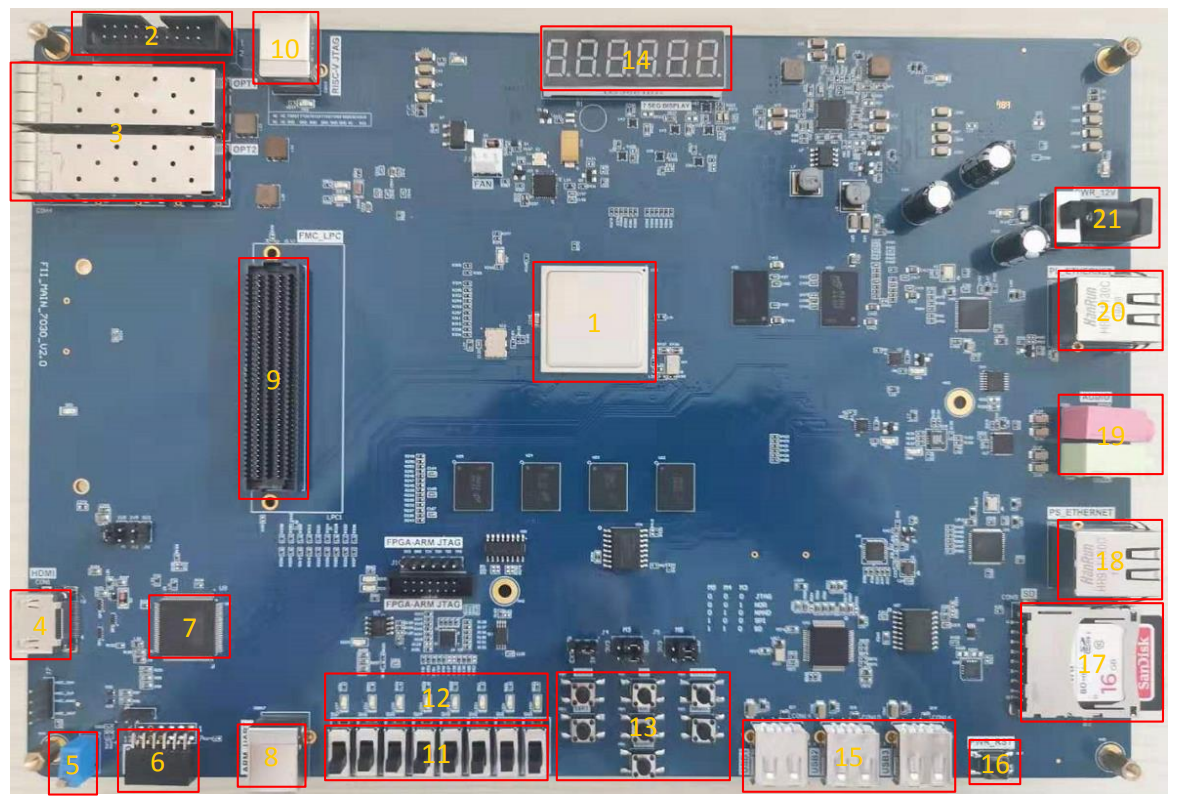

zynq xc7z030 board – FII-PE7030 Experiment 8 – Use of ROM, Study the format of *.coe and how to edit *.coe file to configure the contents of ROM

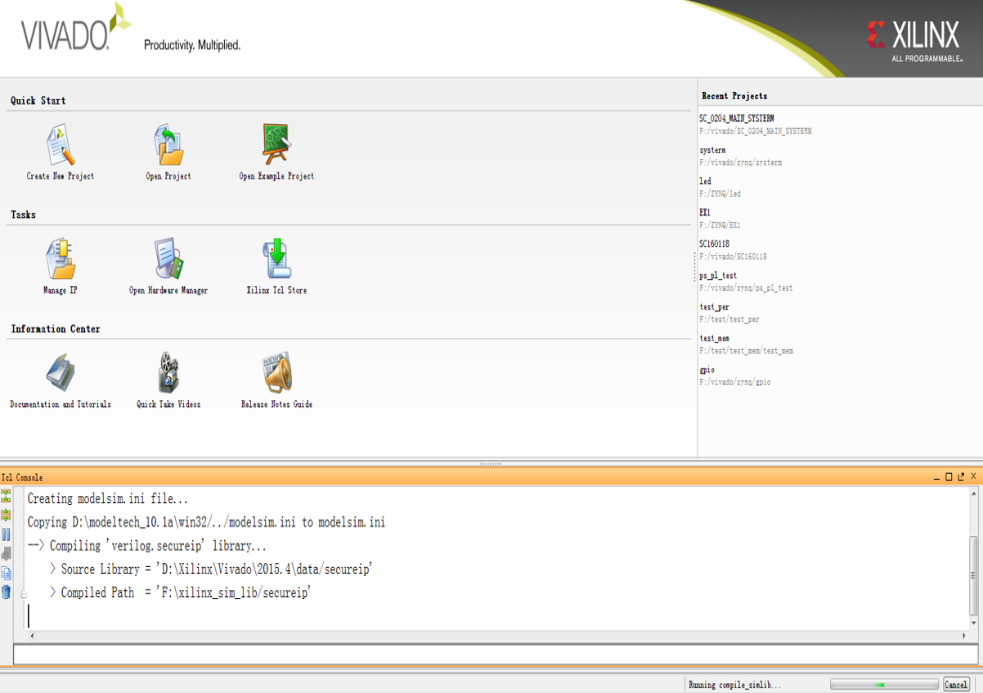

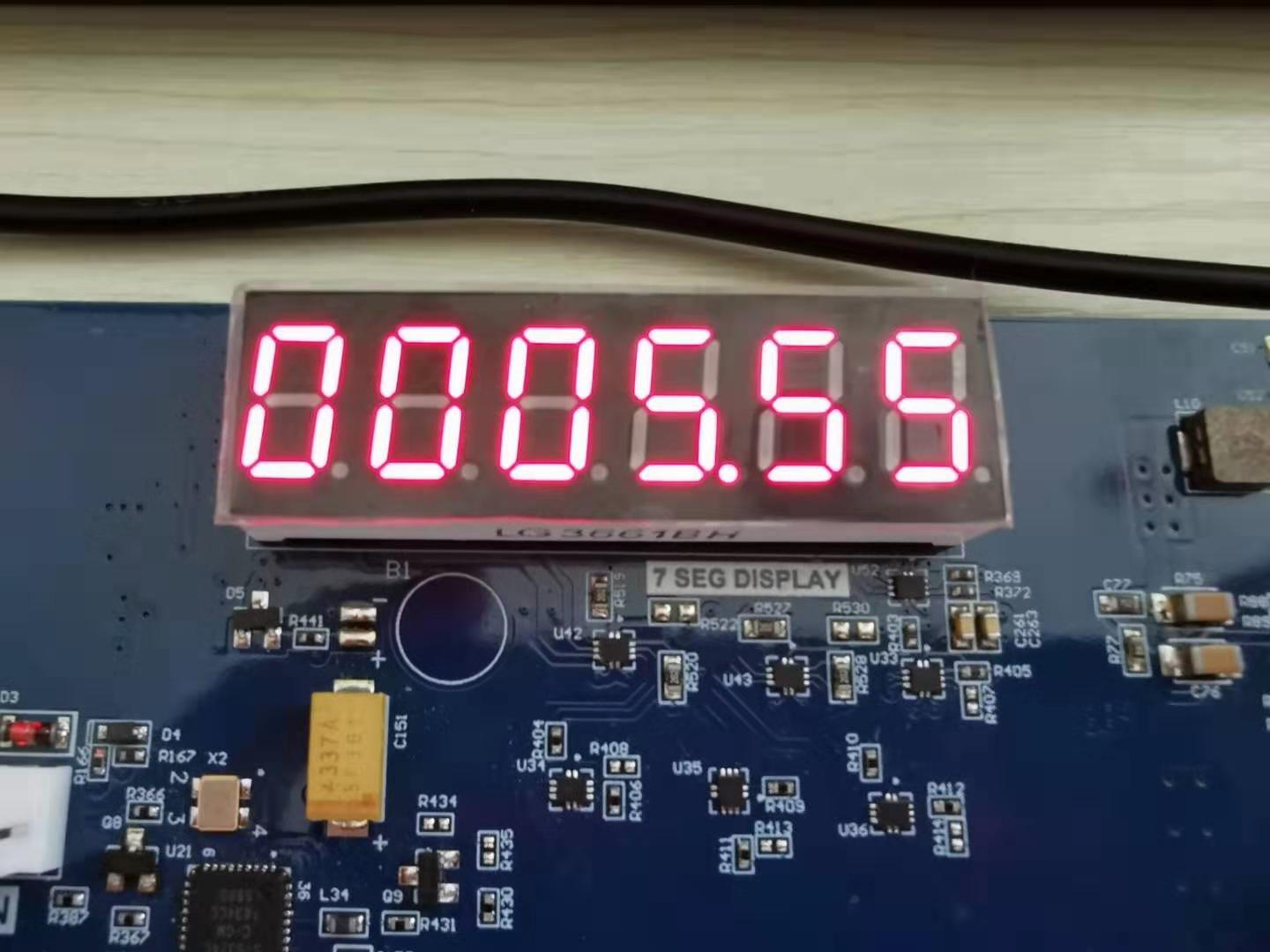

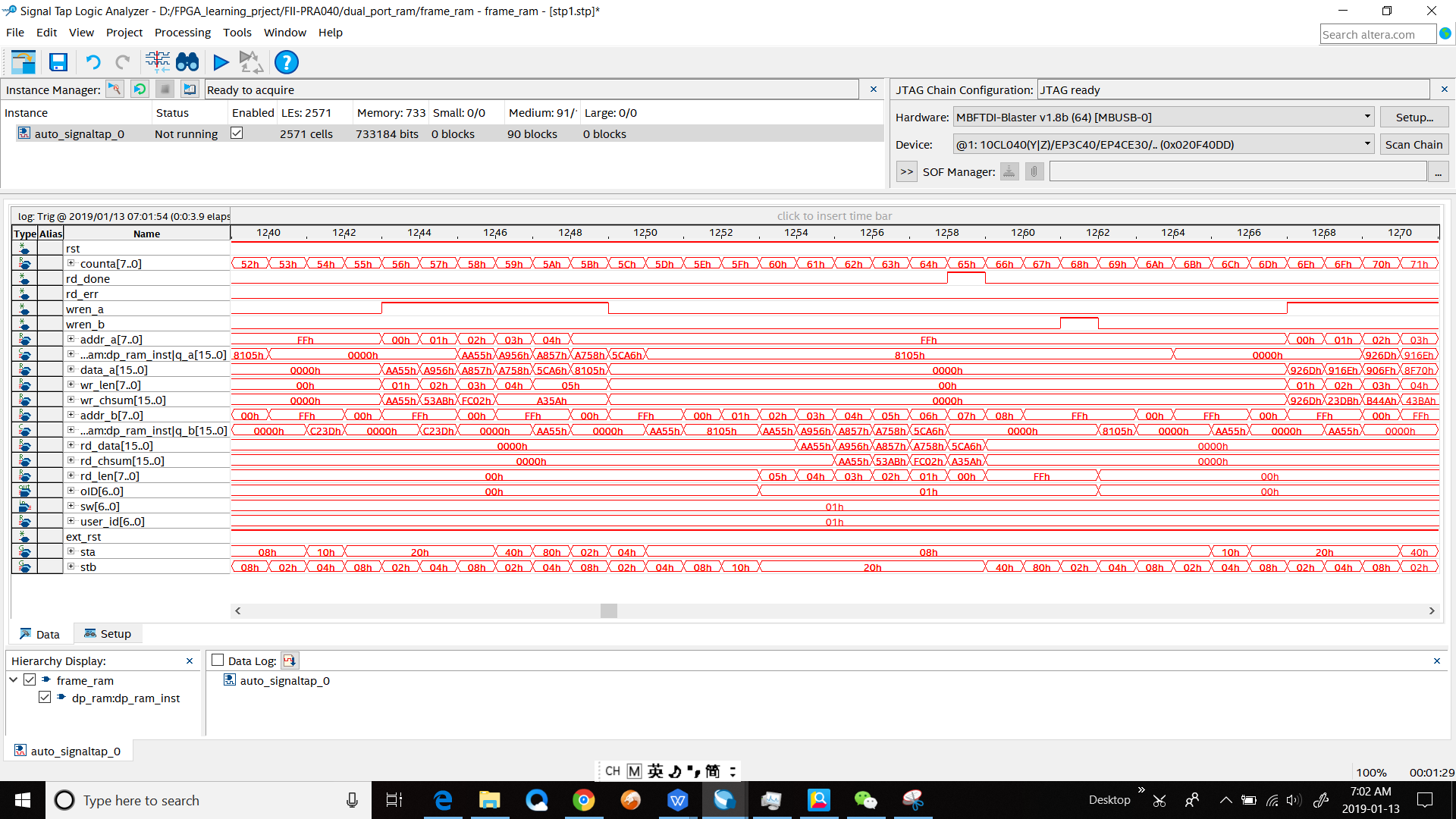

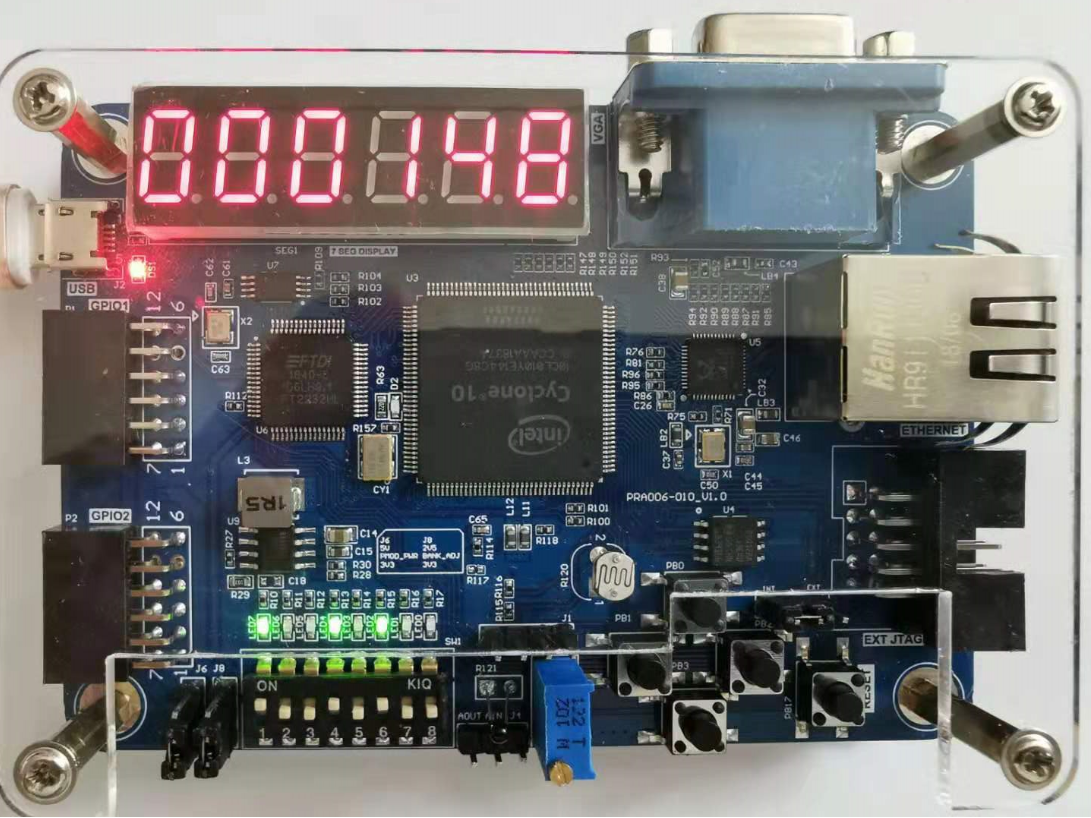

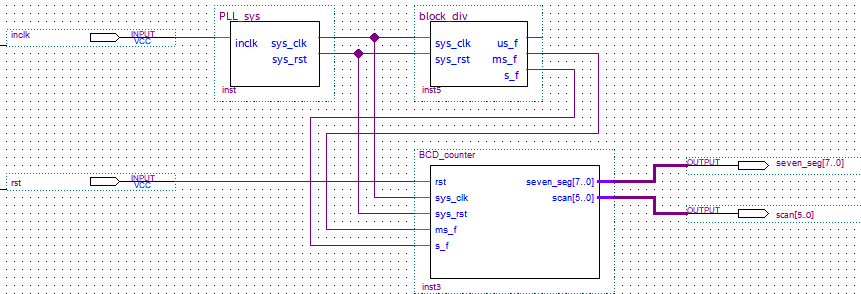

Experiment 8 Use of ROM 8.1 Experiment Objective Study the usage of internal memory block of FPGA Study the format of *.coe and how to edit *.coe file to configure the contents of ROM Learn to use RAM, read and write RAM 8.2 Experiment Implement Design 16 outputs ROM, address ranging 0-255 Interface 8-bit switch input as ROM’s address Segment display illustartes the contents of ROM and require conversion of hexadecimal to BCD output. 8.3 Experiment 8.3.1 Program Design The first step: the establishment of the main program…

Read More